NECź©źņĪóĖŁżż90nmCMOSżŪ2.7Gsps/50mWż╬źšźķź├źĘźÕA-Dź│ź¾źąĪ╝ź┐╝┬ĖĮ

╚∙║┘▓Įż╣żļż╚źąźķż─żŁż¼╗\ż©Īóźóź╩źĒź░övŽ®ż“║ŅżĻż╦ż»ż»ż╩żļėXČĘż“æ]Ū╦ż╣żļżĶż”ż╩A-Dź│ź¾źąĪ╝ź┐övŽ®źóĪ╝źŁźŲź»ź┴źŃż“NECź©źņź»ź╚źĒź╦ź»ź╣ż¼│½╚»ĪóVLSI SymposiumżŪ╚»╔Įż╣żļĪŻż│ż╬Č\Įčż“90nmCMOSźóź╩źĒź░źūźĒź╗ź╣ż╦┼¼├ōĪó╩č┤╣Å]┼┘2.7GźĄź¾źūźļ/╔├ż╚╣ŌÅ]ż╩ż¼żķŠ├õJ┼┼╬üż¼50mWż╚Š»ż╩żż6źėź├ź╚ż╬źšźķź├źĘźÕöĄ(sh©┤)╝░A-Dź│ź¾źąĪ╝ź┐ż“╗Ņ║ŅżĘż┐ĪŻ°BŃ^ż╬ź╚źĻź▀ź¾ź░żŽµ£ż»╗╚ż├żŲżżż╩żżż┐żßĪóÖ┌ŠÅ└Łż¼╣ŌżżĪŻ

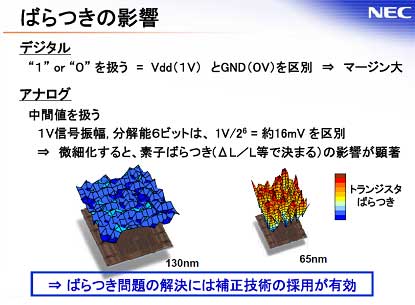

CMOSź╚źķź¾źĖź╣ź┐ż“╚∙║┘▓ĮżĘżŲżżż»ż╦ż─żņĪóź▓Ī╝ź╚─╣ż╩ż╔ż╬źąźķż─żŁż¼Vthż╬źąźķż─żŁż╚żżż├ż┐┼┼╬«Ī”┼┼░Ą├═ż╦Įj(lu©░)żŁż»▒Ųūxż“Ą┌ż▄ż╣ĪŻźŪźĖź┐źļövŽ®ż╚żŽ░ŃżżĪóŲ▒żĖµć┼┘ż╬źąźķż─żŁżŪżŌźóź╩źĒź░övŽ®ż╬╚∙║┘▓Įż╦żŽĖ┬żĻż¼żóż├ż┐ĪŻżŌż┴żĒż¾Īóź▐ź╣ź»æųżŪ▌ö┘ćż╣żļż│ż╚żŽŠ’╝▒żŪżŽżóżļż¼ĪóżĮżņż└ż▒żŪżŽźŪźĖź┐źļövŽ®ż╚Ų▒żĖµć┼┘ż╬źąźķż─żŁż╩żķźóź╩źĒź░övŽ®żŽŲ░║ŅżĘż╦ż»ż»ż╩ż├żŲżĘż▐ż”ĪŻNECź©źņżŽ║ŻövĪóØŖ└Łźąźķż─żŁż“æ]ż┴Š├żĘ╣ńż”żĶż”ż╩A-Dź│ź¾źąĪ╝ź┐ż╬┐ʿʿżövŽ®öĄ(sh©┤)╝░ż“╣═░ŲżĘż┐ĪŻ

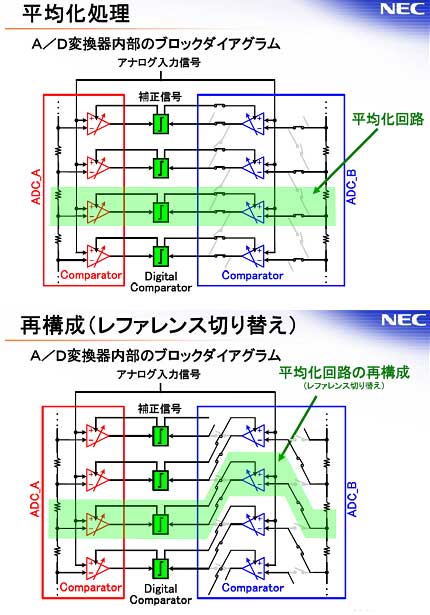

źėźŪź¬żõ▒ŪćĄ▒■├ōż╬A-Dź│ź¾źąĪ╝ź┐żŪżŽĪóźšźķź├źĘźÕöĄ(sh©┤)╝░ż╚Ō}żążņżļ╩┬š`öĄ(sh©┤)╝░ż“╗╚ż”ż│ż╚ż¼¾HżżĪŻż│ż╬öĄ(sh©┤)╝░żŽĪó▓╝░╠źėź├ź╚ż½żķæų░╠źėź├ź╚ż╦ż½ż▒żŲĪó╩¼▓“ē”ż╦▒■żĖżŲź│ź¾źčźņĪ╝ź┐ż“ż║żķż├ż╚╩┬ż┘Īó▐k┼┘ż╦╚µ│ėżĘżŲżżż»öĄ(sh©┤)╝░ż“╗╚ż”ż┐żßĪó╣ŌÅ]ż╬ź│ź¾źąĪ╝ź┐ż╦żĶż»╗╚ż’żņżļĪŻ║Żövż╬żĶż”ż╦╩¼▓“ē”ż¼6źėź├ź╚żŪżóżņżą2ż╬6ŠĶż╣ż╩ż’ż┴64Ė─ż╬ź│ź¾źąĪ╝ź┐ż“╩┬ż┘żļĪŻ

ź│ź¾źčźņĪ╝ź┐ż╦żŽ╣Ō╗@┼┘ż╬┤ØŹ┼┼░ĄĖ╗ż¼ØŁ═ūż╦ż╩żļż¼Īóż│żņż¼┴Ū╗ęźąźķż─żŁż╦▒ŲūxżĄżņżļĪŻżĮż│żŪNECź©źņż¼╣═ż©ż┐ż╬żŽĪó1źėź├ź╚ż╬A-Dź│ź¾źąĪ╝ź┐ż╣ż╩ż’ż┴ź│ź¾źčźņĪ╝ź┐ż“Īó1/64Vcc┼┼░Ą├▒░╠żŪ2Ė─ż║ż─ź┌źóż╦żĘżŲŪ█ÅøżĘĪóżĮżņżŠżņż╬║╣╩¼ż“║╬żĻ╩┐Čč▓Įż╣żļöĄ(sh©┤)╦ĪżŪżóżļĪŻ║╣╩¼żŽźŪźĖź┐źļź│ź¾źčźņĪ╝ź┐żŪ╚µ│ėżĘĪóżŌżĘ║╣╩¼ż¼Įj(lu©░)żŁż╣ż«żļż╩żķµuż╬ź│ź¾źčźņĪ╝ź┐ż╦└┌żĻü÷ż©Īó║Ų╣Į└«żĘ─Šż╣ĪŻż╣ż╩ż’ż┴Īóź┌źóż╬ź│ź¾źčźņĪ╝ź┐ż╬╩┐Ččż╚║Ų╣Į└«Ī╩▌ö┘ćĪ╦ż╚żżż”╣═ż©öĄ(sh©┤)żŪżążķż─żŁż“žō(f©┤)żķż╣ż╚żżż”Ślż└ĪŻ

║Żövż╬övŽ®żŪżŽź│ź¾źčźņĪ╝ź┐ż“65Ė─└▀ÅøżĘż┐ĪŻź│ź¾źčźņĪ╝ź┐ż“└┌żĻü÷ż©żŲ║Ų╣Į└«żĘ─Šż╣╣═ż©öĄ(sh©┤)żŽźßźŌźĻĪ╝ż╬∙N─╣╣Į└«Ī╩źĻź└ź¾ź└ź¾źĘĪ╦ż╦ō¶żŲżżżļĪŻź┌źóż╬ź│ź¾źčźņĪ╝ź┐ż¼∙N─╣ż╦1×┤├ō┴TżĄżņżŲżżżļżĶż”ż╩żŌż╬ĪŻ

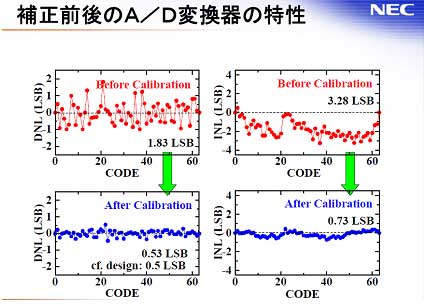

NECź©źņżŽ▌ö┘ćż╣żļØiż╚ĖÕżŪż╬A-Dź│ź¾źąĪ╝ź┐ż╬ØŖ└Łż“╚µ│ėżĘżŲżżżļĪŻźąźķż─żŁĖĒ║╣DNLĪ╩differential non-linearity errorĪ╦ż¼▌ö┘ćØiżŽ1.83LSBĪ╩least significant bitĪ╦ż╚Įj(lu©░)żŁż½ż├ż┐ż¼Īó▌ö┘ćĖÕżŽ0.53LSBż╚╗╚ż©żļźņź┘źļż╦╝²ż▐ż├ż┐ĪŻż▐ż┐ØÖ─Š└■└ŁĖĒ║╣INLĪ╩integral non-linearity errorĪ╦żŽ▌ö┘ćØiż¼3.28LSBż╚╗╚żżØ±ż╦ż╩żķż╩żżż█ż╔Įj(lu©░)żŁż½ż├ż┐ż¼Īó▌ö┘ćĖÕżŽ0.73LSBż╚ż▐ż║ż▐ż║ż╬źņź┘źļż╦╝²ż▐ż├żŲżżżļĪŻ

“£═Ķż╬źšźķź├źĘźÕź│ź¾źąĪ╝ź┐ż└ż╚°BŃ^ż╬ź╚źĻź▀ź¾ź░ż“żĘż╩ż¼żķźąźķż─żŁż“═▐ż©żŲżżż»ż╚żżż”öĄ(sh©┤)╝░ż“╗╚ż”ż│ż╚ż¼¾Hż½ż├ż┐ĪŻżĘż½żŌ┤ØŹ┼┼░ĄĖ╗żŽ╣Ō╗@┼┘ż¼═ūĄßżĄżņżļĪŻż│ż╬ż┐żßĪó─Ńź│ź╣ź╚▓ĮżŪżŁż╩ż½ż├ż┐ĪŻ║Żövż╬Č\Į迎ź╚źĻź▀ź¾ź░ż╬ØŁ═ūż¼ż╩ż»Īó─Ńź│ź╣ź╚▓ĮżĘżõż╣ż»Ēö┴Ķ╬üż¼żóżĻĪóÖ┌ŠÅ└Łż¼╣ŌżżĪŻ╚∙║┘▓Įż╦żĶżļ─ŃŠ├õJ┼┼╬üż╚żżż”┼└żŌĮj(lu©░)żŁżżĪŻ

90nmźūźĒź╗ź╣żŪ║Ņż├ż┐ż│ż╬6źėź├ź╚övŽ®ż╬ź┴ź├źūźĄźżź║żŽ0.36╩┐öĄ(sh©┤)mmż╚Š«żĄż»żŪżŁż┐ĪŻż┴ż╩ż▀ż╦ISSCC2009żŪżŽIntelż¼ź½Ī╝ź═ź«Ī╝źßźĒź¾Įj(lu©░)│žż╚Č”Ų▒żŪĪó45nmCMOSżŪ║Ņż├ż┐7źėź├ź╚A-Dź│ź¾źąĪ╝ź┐ż╬ź┴ź├źūĀC└迎1╩┐öĄ(sh©┤)mmżŌżóż├ż┐ĪŻNECź©źņż╬övŽ®żŪ7źėź├ź╚ż╦│╚─źż╣żļż╩żķź│ź¾źčźņĪ╝ź┐ż╬┐¶ż¼2Ū▄╗\ż©żļż┐żß├▒ĮŃż╦ź┴ź├źūĀC└čżŌ2Ū▄ż╦ż╩żļż╚▓Š─ĻżĘżŲżŌ0.72╩┐öĄ(sh©┤)mmż╦ż╚ż╔ż▐żļĪŻ