┼ņėøĪóż─żżż╦3D-NANDźšźķź├źĘźÕż“×æēä▓ĮĪóBiCSż“║╬├ō

┼ņėøż¼48┴žż╬NANDźšźķź├źĘźÕźßźŌźĻż“3ĘŅ26Ų³ż½żķźĄź¾źūźļĮą▓┘ż╣żļż╚╚»╔ĮżĘż┐ĪŻ128Gźėź├ź╚ż╬×æēäżŪ2źėź├ź╚/ź╗źļ╣Įļ]ż“Ęeż┴Īó┼÷╝ęż╬3╝ĪĖĄźßźŌźĻBiCSČ\ĮčżŪÖ┌ŠÅż╣żļĪŻż│żņżŽźŌź╬źĻźĘź├ź»ż╦źßźŌźĻź╗źļż“āeż╦└čż▀æųż▓żļöĄ╝░żŪĪóżżż’żµżļ3D-ICż╚żŽ░Ńż”ĪŻ

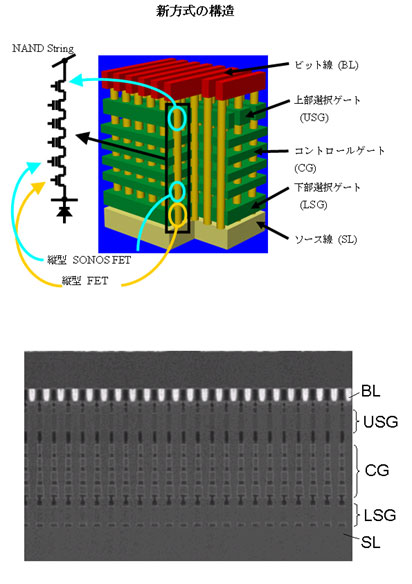

┐▐1ĪĪ┼ņėøż¼│½╚»żĘż┐3╝ĪĖĄNANDźšźķź├źĘźÕBiCSż╬▄ćŪ░ĪĪĮąųZĪ¦┼ņėøźūźņź╣źĻźĻĪ╝ź╣(2007ŃQ6ĘŅ12Ų³)

“£═Ķż╬2╝ĪĖĄNANDźšźķź├źĘźÕż╬źßźŌźĻź╗źļżŽ╩┐ĀCæųż╦▓ŻöĄĖ■ż╦╩┬ż┘ż┐╣Įļ]ż“żĘżŲżżżļż¼Īó3╝ĪĖĄNAND╣Įļ]żŽĪó▓Żż╦╩┬ż┘ż┐ź╗źļż“āeż╦└čżÓżĶż”ż╩Ę┴ż“żĘżŲżżżļĪŻ┐▐1ż╬£u┐¦ż╬┼┼Č╦║Ó╬┴Ī╩ź▌źĻźĘźĻź│ź¾Ī╦ż“āeż╦└čż▀─_ż═ż┐ĖÕĪó▐kĄżż╦Å──╠╣”ż“│½ż▒ĪóźßźŌźĻMOSż╬ź┴źŃź¾ź═źļ║Ó╬┴ż“ļmżß╣■żÓ(┐▐2)ĪŻź╗źļż╦żŽ“£═Ķż╬żĶż”ż╩źšźĒĪ╝źŲźŻź¾ź░ź▓Ī╝ź╚╣Įļ]żŽ╗╚ż©ż╩żżż┐żßĪóźßźŌźĻź╗źļ╣Įļ]żŽ├Ō▓Į╦ņż“Ų│Ų■ż╣żļMNOSż╩ż╔ż╬╣Įļ]ż“║╬żļĪŻ┼ņėøżŽSONOS╣Įļ]ż╦żĘżŲżżżļĪŻ

![┐▐2ĪĪ“£═Ķ╣Įļ]ż╚3╝ĪĖĄNANDźšźķź├źĘźÕ╣Įļ]ż╬╚µ│ėĪĪĮąųZĪ¦┼ņėøźūźņź╣źĻźĻĪ╝ź╣(2007ŃQ6ĘŅ12Ų³)](/archive/editorial/technology/img/TFC150326-01b.jpg)

┐▐2ĪĪ“£═Ķ╣Įļ]ż╚3╝ĪĖĄNANDźšźķź├źĘźÕ╣Įļ]ż╬╚µ│ėĪĪĮąųZĪ¦┼ņėøźūźņź╣źĻźĻĪ╝ź╣(2007ŃQ6ĘŅ12Ų³)

3╝ĪĖĄNANDżŽSamsungż¼└Ķ╣įżĘĪó×æēä▓ĮżŽ▐k║“ŃQ╣įż├ż┐ĪŻSSDżõ╔wöüż╬ź╣ź╚źņĪ╝źĖ├ō²ŗż“┴└ż├ż┐żŌż╬ż└ż¼Īóż╣żŪż╦SSDż╦żŌ┼ļ║▄żĘżŲżżżļ(╗▓╣═½@╬┴1)ĪŻSamsungż╬3D-NANDż╬Ö┌ŠÅżŽż”ż▐ż»żżż├żŲżżż╩żżż╚ż╬ż”ż’żĄż¼żóżĻĪóżĮż╬ż│ż╚ż¼Ą£╝┬ż½ż╔ż”ż½żŽż’ż½żķż╩żżż¼Īó┼ņėøż╚żĘżŲżŽSamsungż╬ĖÕ┐ąż“Ūęż╣żļŚlż╦żŽżżż½ż╩żżĪŻż│ż╬ż┐żßĪó3╝ĪĖĄ▓Įż“Šåżżż└ż╚╔«ŪvżŽż▀żļĪŻ┼ņėøż╬3D-NANDżŽSK HynixżõMicronż╩ż╔żĶżĻżŌęÆż»Īó╚∙║┘▓Įż“═ź└ĶżĘżŲ2╝ĪĖĄ▓Įż“═ź└ĶżĘżŲżżż┐(╗▓╣═½@╬┴2)ĪŻżĘż½żĘĪóż│ż│żŪ╚»╔Įż“Šåżżż└ż╚żżż”ż│ż╚żŽĪóSamsungż╚ż╬║╣ż“ż│żņ░╩æų╣Łż▓żļŚlż╦żŽżżż½ż╩żżż╚żżż”»é┴T╔Į£½żŪżŽż╩żżż½ĪŻż┐ż└żĘĪó╦▄│╩┼¬ż╩╬╠ŠÅżŽ╝Ŗ▓Ķ─╠żĻ═ĶŃQż└żĒż”ĪŻ

┼ņėøż╬źūźņź╣źĻźĻĪ╝ź╣ż╦żĶżņżąĪóBiCS╣Įļ]żŽ2016ŃQØi╚Šż╦ļA╣®═Į─Ļż╬Ų▒╝ę╗═Ų³▌x╣®Šņ┐ĘÄźŗī2×æļ]┼’żŪżŌÖ┌ŠÅż╣żļ═Į─Ļż└ż╚żĘżŲżżżļĪŻż─ż▐żĻĪóĮj╬╠Ö┌ŠÅżŽ═ĶŃQż╚żżż”┴T╠ŻżŪżóżļĪŻ

╗▓╣═½@╬┴

1. źĄźÓź╣ź¾Īó3╝ĪĖĄNANDż“64Ė─┼ļ║▄żĘż┐SSDż“╬╠ŠÅ│½╗Ž (2013/08/15)

2. NANDźšźķź├źĘźÕż╬ĘQ╝ęźĒĪ╝ź╔ź▐ź├źūż¼Įą┬Ęż” (2014/08/26)