VLSI Sympo╩¾╣Ī¦Intelż╬Mayberry CTOĪóź│ź¾źįźÕĪ╝ź┐ź╚źņź¾ź╔ż“Ėņżļ

VLSI Symposiumż╬┤─┤╣ų▒ķ2Ų³ų`żŪżŽĪóIntelż╬CTOżŪżóżļMichael MayberryĢ■ż¼Īóź│ź¾źįźÕĪ╝źŲźŻź¾ź░ż╬ĮjżŁż╩╬«żņż╚Įø═Ķż╬öĄĖ■ż╦ż─żżżŲĖņż├ż┐ĪŻźŪĪ╝ź┐ź╗ź¾ź┐Ī╝ż╬ź╚ź▌źĒźĖĪ╝ż¼╩čż’żĻĪó├µ▒¹ż½żķ╩¼Üg▓Įż╬öĄĖ■ż“┐āżĘż┐ĪŻØŁ═ūż╩╚ŠŲ│öüźŪźąźżź╣ż╦żŌ┐©żņĪóGAA╣Įļ]ż╩ż╔ż╬«Ć╚∙║┘▓ĮĪóź┴ź├źūźņź├ź╚ż╦żĶżļ╣ŌĮĖ└č▓ĮĪó3D-IC▓ĮżžĖ■ż½ż”ĪŻźÓĪ╝źóż╬╦Īō¦ż╬żĶż”ż╦ĪóźŪĪ╝ź┐╬╠żŽ3ŃQżŪ2Ū▄╗\ż©żļż╚═ĮĖ└żĘż┐ĪŻ

┐▐1ĪĪIntel Senior VPĘ¾CTO & GM Technology Developmentż╬Mike MayberryĢ■ĪĪĮąųZĪ¦Intel Corp.

ż│żņż½żķż╬╚ŠŲ│öüź│ź¾źįźÕĪ╝źŲźŻź¾ź░żŪ─_═ūż╩ż│ż╚żŽĪóź╣ź▒Ī╝źĻź¾ź░ż└ż▒żŪżŽż╩ż»ĪóżžźŲźĒźūźĒź╗ź├źĄż╬ĮĖ└č▓ĮżõĪóŲ▒╗■║Ū┼¼▓ĮĪóźĮźšź╚ź”ź©źóż¼ż▒ż¾░·ż╣żļźŽĪ╝ź╔ź”ź©źóĪóAIĪ╩┐═╣®ē¶ē”Ī╦Īó═źżņż┐ź│ź¾źįźÕĪ╝ź┐źĒźĖź├ź»ż└ż╚żżż”ĪŻż│żņż▐żŪż╬źĄĪ╝źąĪ╝żõźčźĮź│ź¾ż└ż▒żŪżŽż╩ż»Ī󟻟ļź▐żõĪóźŪźĖź┐źļźŲźņźėż╬żĶż”ż╩źųźĒĪ╝ź╔źŁźŃź╣źŲźŻź¾ź░źĄĪ╝źėź╣Ī╩Netflixż╩ż╔Ī╦Īó┤Ų£åź½źßźķĪóIoTźŪźąźżź╣ż╩ż╔żĄż▐żČż▐ż╩źŪźąźżź╣ż½żķÖ┌ż▀ĮążĄżņżļźŪĪ╝ź┐Ī╩┼D═²żĄżņżŲżżż╩żżźŪĪ╝ź┐Ī¦unstructured dataĪ╦ż¼ż▐ż╣ż▐ż╣╦─Įjż╦╗\ż©żļż┐żßĪóż│żņżķż╬Č\Įčż¼’Lż½ż╗ż╩ż»ż╩żļż╬żŪżóżļĪŻ

żŌż├ż╚É║öü┼¬ż╦Šę▓żĘżĶż”ĪŻ╬Ńż©żąź»źļź▐żŽż½ż─żŲźŽĪ╝ź╔ź”ź©źóż╬ż▀ż└ż├ż┐ĪŻżĮżņż¼ź┐ź»źĘĪ╝ż╬┼ąŠņżŪźĄĪ╝źėź╣ż“─¾ČĪż╣żļżĶż”ż╦ż╩żĻĪó║ŪŖZżŪżŽśOŲ░▒┐┼Šż╦Ė■ż▒ż┐ADASż╬żĶż”ż╦źĄĪ╝źėź╣+Š╩¾ż“┼ļ║▄ż╣żļżĶż”ż╦ż╩ż├ż┐ĪŻżĮżņż╦żĶż├żŲ▓┴├═żŽ╗\Įjż╣żļĪŻ

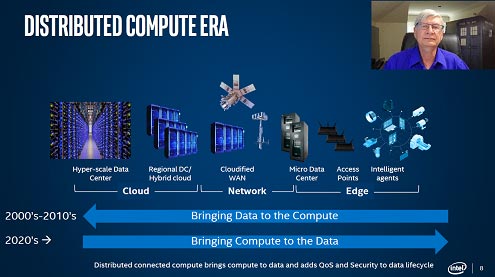

źŪĪ╝ź┐ż╦░Ņżņżļ└ż─cż“żŌż├ż╚żŁżņżżż╦┼D═²ż╣żļż┐żßż╦ĪóźŪĪ╝ź┐ź╗ź¾ź┐Ī╝ż╬ź╚ź▌źĒźĖĪ╝ż¼╩čż’żļż╚MayberryĢ■żŽĖ└ż”ĪŻż│żņż▐żŪż╬├µ▒¹ĮĖĖó┼¬ż╩źŪĪ╝ź┐ź╗ź¾ź┐Ī╝ż½żķżŌż├ż╚╩¼Üg┼¬ż╩źŪĪ╝ź┐ź╗ź¾ź┐Ī╝ż╦╩čż’żļż╚żżż”ż╬ż└ĪŻźŪĪ╝ź┐┼Š┴„ż╬ź│ź╣ź╚żŽź│ź¾źįźÕĪ╝ź┐ź│ź╣ź╚ż“«Ćż©żļżĶż”ż╦ż╩żĻĪóź©ź├źĖżžż╚ŖZż┼ż»ż½żķż└ĪŻż─ż▐żĻĪ󟻟ķź”ź╔ź┘Ī╝ź╣ż╬źŪĪ╝ź┐ź╗ź¾ź┐Ī╝ż½żķ├Ž░Ķż╬źŪĪ╝ź┐ź╗ź¾ź┐Ī╝Īó─╠┐«┤├ŽČ╔ŲŌżŪż╬ź»źķź”ź╔WANżõź©ź├źĖ┤├ŽČ╔żŪż╬źŪĪ╝ź┐ź╗ź¾ź┐Ī╝Ī󿥿ķż╦żŽź©ź├źĖżŪż╬źŪĪ╝ź┐ź╗ź¾ź┐Ī╝ż╩ż╔żžż╚╩¼Ügż╣żļĪ╩┐▐2Ī╦ĪŻ

┐▐2ĪĪźŪĪ╝ź┐ź╗ź¾ź┐Ī╝żŽ├µ▒¹ĮĖĖóĘ┐ż½żķ╩¼ÜgĘ┐żžĪĪĮąųZĪ¦Intel Corp

źŪĪ╝ź┐ź╗ź¾ź┐Ī╝ż¼╩¼Üg▓ĮżĄżņĪó┼D═²żĄżņżŲżżż╩żżźŪĪ╝ź┐ż¼┼D═²żĄżņż╩ż¼żķżŌźŪĪ╝ź┐ż╬╬╠żŽ╗\ż©¶öż▒żļĪŻĄšż╦Ė└ż©żąĪó┼D═²żĄżņżŲżżż╩żżźŪĪ╝ź┐ż╬Ū·╚»ż“╦╔ż░ż┐żßż╦źŪĪ╝ź┐ź╗ź¾ź┐Ī╝ż¼╩¼Üg▓Įż╣żļż╚żŌżżż©żļĪŻ

╩¼Üg▓ĮźŪĪ╝ź┐ź╗ź¾ź┐Ī╝ż╦ż╩żņżąĪóżĮż│ż╦┼ļ║▄żĄżņżļ╚ŠŲ│öüź┴ź├źūżŽĪó«ĆŠ«Ę┐ż╬źŪĪ╝ź┐ź╗ź¾ź┐Ī╝ż╬żĶż”ż╦ĪóCPUż╚GPUĪóDSPĪóNPUĪ╩ź╦źÕĪ╝źķźļź═ź├ź╚ź’Ī╝ź»źūźĒź╗ź├źĄĪ╦ż╩ż╔XPUĪ╩¾H┐¶ż╬░█¹|źūźĒź╗ź├źĄĪ╦ż╦ż╩żļĪŻż│żņżŽĪóź©ź├źĖżŪż╬└ņ├ōźūźĒź╗ź├źĄż╬żĶż”ż╦Īóź╔źßźżź¾ź╣ź┌źĘźšźŻź├ź»ż╩źóĪ╝źŁźŲź»ź┴źŃż“Ęeż─żĶż”ż╦ż╩żļĪŻź©ź═źļź«Ī╝Ė·╬©ż“æųż▓żļż┐żßż└ĪŻ

źžźŲźĒźūźĒź╗ź├źĄźóĪ╝źŁźŲź»ź┴źŃżŽĪó╠┐╬ßź╗ź├ź╚ż¼źūźĒź╗ź├źĄż┤ż╚ż╦żóżĻĪóČ╦żßżŲ╩Ż╗©ż╦ż╩żļĪŻĮĖ└č┼┘ż¼╗\ż╣ż└ż▒żŪżŽż╩ż»ĪóźūźĒź░źķź▀ź¾ź░żŌ╩Ż╗©ż╦ż╩żĻĪó│½╚»┤³┤ųż¼─╣┤³ż╦ż’ż┐żļżĶż”ż╦ż╩żļĪŻżĮżņż└ż▒żŪżŽż╩żżĪŻźßźŌźĻ═Ų╬╠żŌ╦─Įjż╦ż╩żĻĪóŠ├õJ┼┼╬üż¼╦─Įjż╦ż╩żĻż╣ż«żļĪŻ▓├ż©żŲAIź┴ź├źūżŽØŖż╦│žØ{ź┴ź├źūż╬ĮĖ└č┼┘żŽ║Żż╦żŌ╗\żĘżŲ«Ć╩Ż╗©ż╦ż╩żļĪŻż▐żĄż╦ź│ź¾źįźÕĪ╝źŲźŻź¾ź░ź«źŃź├źūż¼żŪżŁżŲżĘż▐ż”ĪŻ

żĮżņż“▓“»éż╣żļ▐kż─ż╬źĮźĻźÕĪ╝źĘźńź¾ż¼źŌźĖźÕźķĪ╝öĄ╝░żŪĪóź│ź¾źįźÕĪ╝źŲźŻź¾ź░żŽźņźżźõĪ╝ż┤ż╚ż╦├Ļō■▓ĮżĘĪó┐Ęż┐ż╩śOŲ░▓Įź─Ī╝źļżŌØŁ═ūż╦ż╩żļĪŻźŽĪ╝ź╔ź”ź©źó┼¬ż╦żŽ3╝ĪĖĄ▓Įżõ2.5╝ĪĖĄ▓Įż╦żĶż├żŲĄĪē”ż┤ż╚ż╦ĮĖ└čżĘżŲżżż»ĪŻż│żņż╦żĶżĻĪó╚ŠŲ│öü×æēäż╦ĮĖ└迥żņżļź╚źķź¾źĖź╣ź┐┐¶żŽ2ŃQżŪŪ▄ż╦ż╩żļż╚żżż”źÓĪ╝źóż╬╦Īō¦ż¼¶öż»ż│ż╚ż╦ż╩żļĪŻ

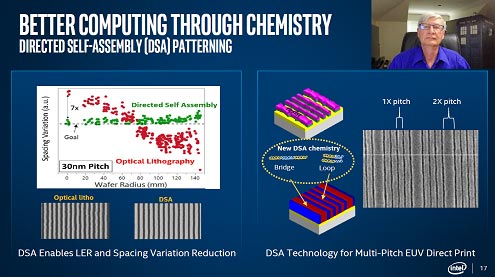

╣ŌĮĖ└č▓ĮČ\Įčż╚żĘżŲĪóź╚źķź¾źĖź╣ź┐żŽGAAĪ╩Gate All AroundĪ╦╣Įļ]ż╦ż╩żĻĪóźčź┐Ī╝ź¾ź╦ź¾ź░żŽ▓Į│ž┼¬ż╩ź╗źļźšźóźķźżź¾Č\Įčż╬DSAĪ╩Directed Self-AssemblyĪ╦Č\ĮčĪ╩┐▐3Ī╦ż“╗╚ż”ż│ż╚żŪź”ź¦Ī╝źŽĀCŲŌźąźķź─źŁż“═▐ż©żļż│ż╚ż¼żŪżŁżļż╚żżż”ĪŻ

┐▐3ĪĪ«Ć╚∙║┘▓Įż╦żŽDSAżŪ×┤▒■ĪĪĮąųZĪ¦Intel Corp

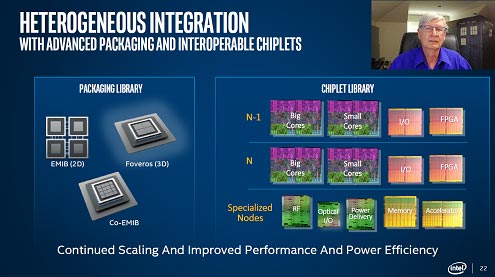

3╝ĪĖĄ▓ĮżŪżŽźßźŌźĻżõźĒźĖź├ź»ż╚ż╬ź╣ź┐ź├ź»ż¼ĖĮ╝┬ż╦ż╩żĻĪóIntelżŽż╣żŪż╦2.5Dż╬EMIBČ\ĮčżõCo-EMIBČ\ĮčĪó3╝ĪĖĄż╬FoverosČ\Įčż“Š”ēä▓ĮżĄż╗żŲżżżļĪŻ║ŪŖZĮą▓┘żĘż┐LakefieldżŽFoverosČ\Įčż“╗╚ż├ż┐żŌż╬Ī╩╗▓╣═½@╬┴1Ī╦ĪŻż│żņżķż╬Č\Į迎ź┴ź├źūźņź├ź╚ż╚żżż”IPź│źóż╬źķźżźųźķźĻż“Ęeż─ż│ż╚ż¼ØŁ═ūż╚ż╩żļĪ╩┐▐4Ī╦ĪŻ

┐▐4ĪĪĮĖ└č┼┘ż“╣Ōżßżļż┐żßż╦2.5DĪó3DČ\Įčżõź┴ź├źūźņź├ź╚Č\Įčż“╗╚ż”ĪĪĮąųZĪ¦Intel Corp

ż│żņżķż“┴╚ż▀╣ńż’ż╗żŲĪóIntelż╬FPGAżŽź┴ź├źūźņź├ź╚żõHBMĪ╩High Bandwidth MemoryĪ╦źŌźĖźÕĪ╝źļż“2.5Dźčź├ź▒Ī╝źĖż╦Ų■żņż┐żĻĪó3╝ĪĖĄż╬Lakefieldż╚┴╚ż▀╣ńż’ż╗ż┐żĻż╣żļżĶż”ż╩źŽźżźŲź»źčź├ź▒Ī╝źĖż¼─_═ūż╩╗■┬Õż╦ż╩żļĪŻ

ż│ż╬└ĶĪóźŽĪ╝ź╔ź”ź©źóż╚źĮźšź╚ź”ź©źóż╬Č”Ų▒┐╩▓Įż¼ØŁ═ūż╦ż╩żļĪŻ“£═Ķż╬źšź®ź¾ź╬źżź▐ź¾Ę┐ź│ź¾źįźÕĪ╝źŲźŻź¾ź░ż½żķźŪźŻĪ╝źūźķĪ╝ź╦ź¾ź░Š}╦ĪĪ󿥿ķż╦źėź├ź░źŪĪ╝ź┐ż╬▓“└Žż╦ØŁ═ūż╩ź░źķźš▓“└ŽĪ╩ź░źķźšż╬─║┼└żõź©ź├źĖż╚ż╬┤žĘĖż“Ė½Įąż╣Š}╦ĪĪ╦Īó┐═┤ųż╬Ų¼╦Nż╬╗┼┴╚ż▀ż“╠Ž╩’ż╣żļź╦źÕĪ╝źĒźŌĪ╝źšźŻź├ź»Īó║ŪĮ¬┼¬ż╦żŽ╬╠╗ęź│ź¾źįźÕĪ╝źŲźŻź¾ź░żžż╚Ė■ż½ż”ż└żĒż”ĪŻż┐ż└żĘĪó╬╠╗ęź│ź¾źįźÕĪ╝źŲźŻź¾ź░żŽ2030ŃQ░╩æTż╦ż╩żļż╚żżż”ĪŻ

IntelżŽż│żņżķż╬┐ʿʿżźóĪ╝źŁźŲź»ź┴źŃż╬ź│ź¾źįźÕĪ╝źŲźŻź¾ź░Š}╦Īż“╗ŅżĘżŲż¬żĻĪóżĮż╬║żžMżĄż“╚®żŪ┤ČżĖżŲżżżļż½żķż│żĮĪóżĮż╬š{▀`┤Čż¼ż’ż½żļż╬żŪżŽż╩żżż└żĒż”ż½ĪŻ

╗▓╣═½@╬┴

1. 3D-ICż¼żżżĶżżżĶźčźĮź│ź¾ż╦║▄żļ╗■┬Õżž (2020/06/16)