źšźĪź”ź¾ź╔źĻż¼╝ĪĪ╣ż╚źĘź▀źÕźņĪ╝źĘźńź¾ź┘ź¾ź└Ī╝ż╚┴╚żÓ═²Įy

ż│żņż▐żŪ╚ŠŲ│öüŠÅČ╚ż╚żŽ▒’ż¼Ū÷ż½ż├ż┐Īó3D-CADż╚źĘź▀źÕźņĪ╝źĘźńź¾ż╬ź┘ź¾ź└Ī╝ż¼└čČ╦┼¬ż╦╚ŠŲ│öüŠÅČ╚ż╦żõż├żŲżŁżŲżżżļĪŻ2.5D/3D-ICżõź┴ź├źūźņź├ź╚╝┬äóż╩ż╔żŪ┐¶├═╝ŖōQźĘź▀źÕźņĪ╝źĘźńź¾ż¼└▀╝Ŗ╗■ż╦’Lż½ż╗ż╩ż»ż╩ż├żŲżŁż┐ż½żķż└ĪŻźĘź▀źÕźņĪ╝źĘźńź¾ź┘ź¾ź└Ī╝ż╬Ansysż¼TSMCżõGlobalFoundriesĪóSamsungźšźĪź”ź¾ź╔źĻŗ╠ńĪóIntelźšźĪź”ź¾ź╔źĻŗ╠ńĪóUMCż╩ż╔ż╚╝ĪĪ╣ż╚─¾Ę╚ż“╚»╔ĮżĘżŲżżżļĪŻ

![┐ʿʿż╚ŠŲ│öüČ\Įčż╦żĶżĻ╣ŌÅ]▓ĮĪóĮjæä╠Ž▓ĮĪó─Ń┼┼╬ü▓Įż¼¶öż» / Ansys](/archive/editorial/industry/img/20231220-Anysys_3D.png)

┐▐1ĪĪ╚ŠŲ│öü╝┬äóż¼3╝ĪĖĄ▓ĮżĘĪóźĘź▀źÕźņĪ╝źĘźńź¾ż╩żĘż╦║Ū┼¼▓“ż¼įużķżņż╩ż»ż╩żļ ĮąųZĪ¦Ansys

ż╚żĻż’ż▒ĪóTSMCżŽEDAź┘ź¾ź└Ī╝źėź├ź░ź╣źĻĪ╝ż╚żŽź©ź│źĘź╣źŲźÓż“Ę┴└«żĘżŲżżżļż¼Īóż│ż│ż╦Ansysż“▓├ż©ż┐ĪŻTSMCżŽ└Ķ├╝źčź├ź▒Ī╝źĖź¾ź░Č\ĮčżŪźĘź▀źÕźņĪ╝źĘźńź¾ź┘ź¾ź└Ī╝ż╬─_═ū└Łż“ē¶ż├żŲżżżļż½żķż└ĪŻ╚ŠŲ│öüČ\Į迎źūźņĪ╝ź╩ź╚źķź¾źĖź╣ź┐ż½żķFinFETżõGAAĪ╩Gate All AroundĪ╦FETż╬żĶż”ż╦3╝ĪĖĄ▓Įżžż╚┐╩·tżĘĪóŪ█└■┴žżŪżĄż©┐«ęÄ┴žż╚┼┼Ė╗┴žż“ź”ź¦Ī╝źŽ─źżĻ╣ńż’ż╗Š}╦Īż╩ż╔żŪ╣Į└«ż╣żļżĶż”ż╩öĄĖ■ż╦Ė■żżżŲżżżļżĶż”ż╦ĪóźŌź╬źĻźĘź├ź»ICżŪżĄż©3╝ĪĖĄ▓Įż╬öĄĖ■ż¼£½│╬ż╦ż╩ż├żŲżżżļĪ╩┐▐1Ī╦ĪŻż▐żĘżŲżõ2.5Dżõ3Dż╬ICż╚ż╩żļż╚ź┴ź├źūż“TSVĪ╩Through Silicon ViaĪ╦ż╩ż╔żŪ─_ż═żŲżżż»żĶż”ż╦ż╩żļĪŻÖ┌└«AIęŖ═ūżŪŠåÅ]ż╦ęŖ═ūż¼╣Ōż▐ż├żŲżżżļĪó3╝ĪĖĄ╣Įļ]ż╬HBMĪ╩High Bandwidth MemoryĪ╦żŪżŽĪó╩Ż┐¶ż╬DRAMź┴ź├źūż╚ź│ź¾ź╚źĒĪ╝źķź┴ź├źūż“─_ż═żŲżżżļż¼Īóż│ż│żŪżŽ┼┼╬üż½żķż╬ÕXż╦żĶż├żŲĄĪ│Ż┼¬ż╩▒■╬üż¼╚»Ö┌ż╣żļĪŻź┴ź├źūżõ┤łżŪż╬╚┐żĻżõ│õżņż¼Ö┌żĖżļźĻź╣ź»ż¼ĮążŲż»żļĪŻ

┼┼Č╦╣Įļ]żŪżŌCuźįźķĪ╝Ų▒╗╬ż“ź▐źżź»źĒźąź¾źūż╩ż╔żŪ└▄¶öżĘżŲżżżļż¼ĪóÕX▒■╬üż“▓“└Žż╣żļż┐żßż╦źąź¾źūż╬Ę┴ėXźĘź▀źÕźņĪ╝źĘźńź¾ż¼ØŁ═ūż╦ż╩żļĪŻż│ż╬źąź¾źūż¼ź©źņź»ź╚źĒź▐źżź░źņĪ╝źĘźńź¾ż“ÅŚż│ż╣ż╚żŌĖ└ż’żņżŲżżżļĪŻżĄżķż╦Īó┤¾Ö┌Ė·▓╠ż╦żĶżļźĘź░ź╩źļźżź¾źŲź░źĻźŲźŻżŌ╠õ¼öż╦ż╩ż├żŲż»żļĪŻ╣ŌÅ]ź╣źżź├ź┴ź¾ź░Ų░║ŅżĄż╗żļż╚┐¶╝åĪó┐¶╗hż╦żŌż╩żļTSV┼┼Č╦ż╦żĶżļ┼┼╝¦─cź½ź├źūźĻź¾ź░ż¼ÅŚżŁĪóŲ░║Ņż¼╔įŖW─Ļż╦ż╩żļĪŻ

ź┴ź├źūż“╝┬äóż╣żļØiż╦ĪóźĘź▀źÕźņĪ╝źĘźńź¾żŪ│╬Ū¦ż╣żļØŁ═ūż¼żóżļĪŻÕXżõ┼┼╝¦─cĪóĄĪ│ŻŽ─ż╩ż╔ż╬ر═²ĖĮō■ż“źŌźŪźļ▓ĮżĘżŲźĘź▀źÕźņĪ╝źĘźńź¾ż╣żļ└ņ╠ń▓╚ż¼═▀żĘżżĪŻAnsysż¼ż│ż╬└ņ╠ń▓╚żŪżóżļĪŻĪų┐õ╬╠żŪżŽż╩ż»źĘź▀źÕźņĪ╝źĘźńź¾ż“┘ćżĘżżöĄ╦ĪżŪ╣įż”ż│ż╚ż¼─_═ūĪūż╚Ansysż╬Chief Technologistż“ē»żßżļChristophe BianchiĢ■Ī╩┐▐2Ī╦żŽĮęż┘żļĪŻ

┐▐2ĪĪAnsys╝ę Chief Technologistż╬Christophe BianchiĢ■

AnsysżŽ└╬ż½żķĪ󿥿▐żČż▐ż╩ر═²ĖĮō■ż╦×┤żĘżŲźŌźŪźļż“╬®żŲöĄµć╝░żŪ╝ŖōQĮĶ═²żĘżŲżŁż┐ĪŻż╚ż│żĒż¼Īó╚ŠŲ│öüź┴ź├źūæųżŪżŽżĄż▐żČż▐ż╩Š«żĄż╩ŠņĮĻżŪż╬┼┼╬üŠ├õJżõĪó╗■┤ų┼¬ż╦ŠņĮĻż╬öĪŲ░ż╩ż╔╩Ż╗©ż╩ÅUżŪż╬źŌźŪźļż“╬®żŲżĶż”ż╚ż╣żļż╚żĮż╬╝ĪĖĄż¼4Īó5Īó6╝ĪĖĄżžż╚╗\ż©żŲżżż»ĪŻż│ż”ż╩żļż╚Ansysż╚żżż©ż╔żŌźŌźŪźļż“╬®żŲżļż│ż╚ż¼╩Ż╗©ż╦ż╩żļĪŻ╩Ż╗©ż╩ÅUżŪżŽ┐¶10ŃQØiż½żķźŌź¾źŲź½źļźĒŠ}╦Īż╩ż╔ż¼╗╚ż’żņżŲżŁż┐ż¼ĪóBianchiĢ■ż╦żĶżļż╚ĪóĪųźŌź¾źŲź½źļźĒźĘź▀źÕźņĪ╝źĘźńź¾ż└ż╚ż╗żżż╝żż4╝ĪĖĄµć┼┘żĘż½╝ŖōQżŪżŁż╩żżĪŻżĄżķż╦╩Ż╗©ż╦ż╩żļż╚░ę╬üż“╚»Ä¦ż╣żļż╬ż¼AI/MLĪ╩ĄĪ│Ż│žØ{Ī╦ż└ĪūĪóż╚Ė└ż”ĪŻ

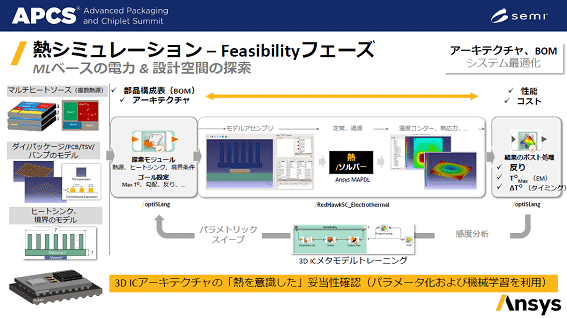

ż│żņż▐żŪż╬źĘź▀źÕźņĪ╝źĘźńź¾└▀╝ŖŠ}╦Īż“╣═ż©─ŠżĘĪóMLż“īÖ├ōżĘż╩ż▒żņżąÕXżõźĘź░ź╩źļźżź¾źŲź░źĻźŲźŻż“╣═╬ĖżĘż┐övŽ®└▀╝ŖżŽżŪżŁż╩ż»ż╩żļż╚BianchiĢ■żŽĮęż┘żļĪŻMLżŪŲ■Įą╬ü┤žĘĖż“į~┴Ū▓ĮżĘĪóźßź┐źŌźŪźļż“║Ņż├żŲ│žØ{ż“Ę½żĻ╩ųż╣Ī╩┐▐3Ī╦ĪŻØŖż╦3╝ĪĖĄICżŪżŽÕXż╬╠õ¼öż¼─_═ūż╦ż╩żļż╚Īó3╝ĪĖĄICż“Š}²Xż▒żļźšźĪź”ź¾ź╔źĻ┤žĘĖŪvżŽĮęż┘żŲżżżļĪŻ

┐▐3ĪĪMLĪ╩ĄĪ│Ż│žØ{Ī╦ż“ŠW├ōżĘżŲ╩Ż╗©ż╩┤žĘĖ└Łż“į~┴Ū▓Įż╣żļĪĪĮąųZĪ¦Ansys

AnsysżŽĪó5ż─ż╬ź│źóź│ź¾źįź┐ź¾ź╣ż╚żżż”ż┘żŁ├ņĪ╩źįźķĪ╝Ī╦ż“Ęeż├żŲżżżļĪŻż╣ż╩ż’ż┴ź▐źļź┴ż╩ر═²│žżõżĄż▐żČż▐ż╩źŌźŪźļĪóHPCĪ╩High Performance ComputingĪ╦ĪóAI/MLĪ󟻟ķź”ź╔żõźµĪ╝źČĪ╝ź©ź»ź╣ź┌źĻź©ź¾ź╣ĪóżĮżĘżŲźŪźĖź┐źļź©ź¾źĖź╦źóźĻź¾ź░ż╬5ż─ż└ĪŻź»źķź”ź╔żõMLż╩ż╔ż“Ņ~╗╚żĘżŲ║Ū╬╔ż╬źĮźĻźÕĪ╝źĘźńź¾ż“─¾ČĪż╣żļż╚BianchiĢ■żŽČ╗ż“─źżļĪŻ