SamsungĪó32Gźėź├ź╚ DRAM│½╚»żŪĪó╝┬Øó╦Īż“12nmĄķż╚╔ĮĖĮ

Samsung Electronicsż¼12nmĄķż╬╚∙║┘▓ĮČ\Įčż“╗╚ż├żŲ32Gźėź├ź╚DDR5 DRAMż“│½╚»żĘż┐ĪŻ╝┬Øó╦Īż╬12nmż╚żżż”╔ĮĖĮż“╚ŠŲ│öüźßĪ╝ź½Ī╝ż¼żĘż┐ż│ż╚żŽż│żņż¼ĮķżßżŲĪŻż│żņż▐żŪźßźŌźĻźßĪ╝ź½Ī╝żŽ20nm░╩▓╝ż╬źūźĒź╗ź╣ż“1x nmĪó1y nmĪó1z nmĪó1α nmĪó1β nmĪó1γ nmĪóż╚1Ī┴2nmż║ż─╣’ż¾żŪżŁż┐ĪŻźĒźĖź├ź»źßĪ╝ź½Ī╝żŽĪó14/16nmźūźĒź╗ź╣ż½żķ10nmĪó7nmĪó5nmĪó4nmĪó3nmż╚Ō}ż¾żŪżŁż┐ż¼Īó╝┬Øó╦ĪżŽ14Ī┴13nmżŪ┘Vż▐ż├ż┐ż▐ż▐ż└ĪŻ

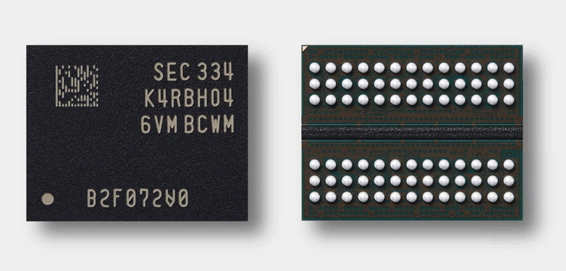

┐▐1ĪĪSamsungż¼│½╚»żĘż┐32Gźėź├ź╚DDR5 DRAM ĪĪĮąųZĪ¦ Samsung Electronics

ż│żņż▐żŪźĒźĖź├ź»żŪżŽ14/16nmźūźĒź╗ź╣ż½żķ╝┬Øó╦Īż╚ĮjżŁż»ż½ż▒▀`żņżŲżŁż┐ĪŻ┐¶ŃQØiż╦żŽIntelż╬10nmźūźĒź╗ź╣ż╚TSMCż╬7nmźūźĒź╗ź╣ż╚żŽż█ż▄┼∙żĘżżĪóż╚Ė└ż’żņżŲżżż┐ĪŻżĘż½żĘĪóż╔ż┴żķżŌ┘ć│╬ż╩Øó╦Īż“╔ĮĖĮżĘżŲżżż╩żżĪŻ10nm╩šżĻż½żķĪó├▒░╠ĀC└č┼÷ż┐żĻż╬ź╚źķź¾źĖź╣ź┐┐¶żŪ╚∙║┘▓Įż“╔ĮĖĮż╣żļżĶż”ż╦ż╩ż├żŲżŁż┐ż½żķż└ĪŻ├▒░╠ĀC└č┼÷ż┐żĻż╬ź╚źķź¾źĖź╣ź┐┐¶żŪżŽTSMCż╬7nmźūźĒź╗ź╣ż╚Intelż╬10nmźūźĒź╗ź╣żŽż█ż▄Ų▒żĖż╩ż╬żŪżóżļĪŻ

╚∙║┘▓Įż¼┘Vż▐ż├ż┐║ŪĮjż╬═²ĮyżŽĪóø]ź┴źŃź¾ź═źļĖ·▓╠żŪźūźņĪ╝ź╩ź╚źķź¾źĖź╣ź┐ż╬ź▓Ī╝ź╚─╣ż¼Ė┬─cż╦═ĶżŲż¬żĻĪ󿥿ķż╦Ū█└■╔²ż╚Ū█└■┤ų│ųżŌ10nm░╩▓╝ż╬Øó╦Īż“ĪóźĻźĮź░źķźšźŻČ\Įčż“╗╚ż├żŲ┘ć│╬ż╦└┌żņż╩ż»ż╩ż├żŲżŁż┐ż½żķż└ĪŻMOSź╚źķź¾źĖź╣ź┐żŽFinFETżõGAAĪ╩Gate All AroundĪ╦╣Įļ]żŪźĻĪ╝ź»┼┼╬«ż“═▐ż©żļżĶż”ż╦ż╩ż├ż┐ż¼ĪóŪ█└■╔²ż╚┤ų│ųżŽ╚∙║┘▓Įż╦×┤▒■żŪżŁż╩ż»ż╩ż├ż┐ĪŻMicronż¼1βnmźūźĒź╗ź╣ż╬DRAM│½╚»ż“║“ŃQ11ĘŅż╬ź¬ź¾źķźżź¾ĄŁŪv└Ō£½▓±żŪ╚»╔ĮżĘż┐╗■Ī╩╗▓╣═½@╬┴1Ī╦Īó╔«ŪvżŽē¶żķż¾┤ķżĘżŲ1βż╚żŽ▓┐nmż½ż╚ä®╠õżĘżŲż▀ż┐ĪŻMicronżŽ13nm░╩▓╝Īóż╚┼·ż©żŲżżżļĪŻ

╚ŠŲ│öüż╬╚∙║┘▓Įż╬┐╩▓ĮżŽ22nmż▐żŪżŽż█ż▄Ū█└■╔²ż╚Ū█└■┤ų│ųż“2/3ż║ż─╚∙║┘▓Įż╣żļż│ż╚żŪź┴ź├źūĀC└čż╬╗\▓├żŌ▓├╠ŻżĘżŲĮĖ└č┼┘ż“2Ū▄ż╦æųż▓żŲżŁż┐ĪŻż│ż╬ż┐żßĪó╚∙║┘▓Įż╬┐╩▓Įż╚źÓĪ╝źóż╬╦Īō¦ż╚żŽŲ▒▐k£åżĄżņżļżĶż”ż╦ż╩ż├żŲżŁż┐ĪŻżĘż½żĘĪóźÓĪ╝źóż╬╦Īō¦żŽĪó▐kż─ż╬ĮĖ└čövŽ®ź┴ź├źūż╦ĮĖ└迥żņżļź╚źķź¾źĖź╣ź┐┐¶żŽ18Ī┴24ź½ĘŅż┤ż╚ż╦Ū▄╗\żĘżŲżżż»Īóż╚żżż”─Ļ▒IżŪżóżĻĪó╚∙║┘▓Įż╚żŽ─Š└▄┤žĘĖż╩ż½ż├ż┐ĪŻ

ż╚ż│żĒż¼ĪóSPI▓±µ^Ė┬─Ļź╗ź▀ź╩Ī╝ĪųTSMCĖ”ē|ĪūżŪŠę▓żĘż┐żĶż”ż╦Ī╩╗▓╣═½@╬┴2Ī╦ĪóŪ█└■╔²ż╚Ū█└■┤ų│ųżŪ╔ĮĖĮżĄżņżŲżżż┐ź╣ź▒Ī╝źĻź¾ź░ō¦ż“źĻź╦źóź╣ź▒Ī╝źĻź¾ź░ż╚Ō}żėĪóĀC└č┼÷ż┐żĻż╬ź╚źķź¾źĖź╣ź┐┐¶żŪ╔ĮĖĮż╣żļż│ż╚ż“ź©źĻźóź╣ź▒Ī╝źĻź¾ź░ż╚Ō}żųżĶż”ż╦ż╩ż├żŲżŁż┐ĪŻTSMCż╚Š’ż╦▐kĮ’ż╦╩Ōż¾żŪżŁż┐źšźĪźųźņź╣źßźŌźĻ┤ļČ╚Etron Technologyż╬CEOżŪżóżļNicky LuĢ■żŽĪóĪųTSMCżŽźĻź╦źóź╣ź▒Ī╝źĻź¾ź░ż½żķź©źĻźóź╣ź▒Ī╝źĻź¾ź░ż“ż╚żļżĶż”ż╦╩čż’ż├ż┐ĪūĪóż╚ĪųKIT/Symetrix International Symposium 2022ĪūĪ╩╗▓╣═½@╬┴3Ī╦ż╬╣ų▒ķż╬├µżŪĮęż┘żŲżżżļĪŻ

TSMCż“żŽżĖżßż╚ż╣żļĪų╚ŠŲ│öü×æļ]ĪūźßĪ╝ź½Ī╝ż¼20nm░╩▓╝ż╬źūźĒź╗ź╣ż“╝┬Øó╦ĪżŪ╔ĮĖĮż╣żļż╚ĪóźßźŌźĻżŌźĒźĖź├ź»żŌźŲź»ź╬źĒźĖĪ╝ż╬┐╩▓Įż¼┐╩ż¾żŪżżż╩żżżĶż”ż╦Ė½ż©żŲżĘż▐ż”ĪŻż│ż╬ż┐żßĪóźßźŌźĻźßĪ╝ź½Ī╝żŽĪó20nmż½żķ19Ī┴18nmż╦öĪ╣įż╣żļż╚1x nmźūźĒź╗ź╣ż╚╔ĮĖĮżĘĪóźĒźĖź├ź»źßĪ╝ź½Ī╝żŽ14/16nmż½żķ10nmżõ7nmż╚╔ĮĖĮżĘż┐ĪŻż▐żļżŪ╚∙║┘▓ĮźŲź»ź╬źĒźĖĪ╝ż¼ż║ż├ż╚¶öżżżŲżżżļżĶż”ż╦Ė½ż©żļĪŻż└ż½żķTSMCżŽ╝┬Øó╦Īż“»éżĘżŲĖ└ż’ż╩ż½ż├ż┐ĪŻź©źĻźóź╣ź▒Ī╝źĻź¾ź░żŪżĄż©ĪóTSMCżŽźŪź¾źĘźŲźŻź╣ź▒Ī╝źĻź¾ź░Ī╩Density ScalingĪ╦ż╚╔ĮĖĮżĘż┐żĻĪóIntelżõimecż╩ż╔żŽDTCOĪ╩Design Technology Co-optimizationĪ¦└▀╝Ŗż╚źūźĒź╗ź╣ż╬Ų▒╗■║Ū┼¼▓ĮĪ╦ż╚╔ĮĖĮżĘżŲżŁż┐ĪŻ

║ŻövżŽżĖżßżŲSamsungżŽ╝┬Øó╦Īż╬12nmĄķźßźŌźĻż╚╔ĮĖĮżĘż┐ĪŻżŌżŽżõĪó1γ nmż▐żŪżõż├żŲżŁż┐░╩æųĪó╝┬Øó╦Īż“ĮążĄżČżļż“įuż╩ż»ż╩ż├ż┐ż┐żßżŪżóżĒż”ĪŻ

żĄżŲĪóSamsungżŽ╚∙║┘▓Įż╦żĶż├żŲźßźŌźĻż╬ĮĖ└č┼┘ż“32Gźėź├ź╚ż╚Ū▄╗\żĄż╗ż┐ż│ż╚żŪĪó│½╚»żĘż┐DRAMźŌźĖźÕĪ╝źļżŽĪóź└źżĪ╩ŅBż╬ź┴ź├źūĪ╦ż“└čż▀─_ż═żļ┴ž┐¶ż¼╚Š╩¼żŪ║čżÓżĶż”ż╦ż╩żĻĪó╠±▓ż╩TSVĪ╩Through Silicon ViaĪ╦źūźĒź╗ź╣ż“╗╚ż’ż║ż╦║čż¾ż└ż╚żżż”ĪŻż│żņż╦żĶżĻŠ├õJ┼┼╬üż“10%║’žōżŪżŁż┐ż╚żĘżŲżżżļĪŻ12nmØó╦Īż╬├Ż└«ż╦╗╚ż├ż┐źĻźĮź░źķźšźŻż¼EUVż½ArFķ]┐╗ź▐źļź┴źčź┐Ī╝ź╦ź¾ź░ż½ż╦ż─żżżŲżŽ£½żķż½ż╦żĘżŲżżż╩żżĪŻ

żĘż½żŌ╚∙║┘▓ĮČ\ĮčżŪĮĖ└č┼┘ż“Ū▄╗\żŪżŁż┐ż│ż╚ż½żķ1TBż╬źßźŌźĻźŌźĖźÕĪ╝źļż╬╠Oż¼│½ż▒ż┐ż╚żĘżŲżżżļĪŻ1TBż╬Įj═Ų╬╠ż└ż╚Ö┌└«AIĖ■ż▒ż╬Įj═Ų╬╠źßźŌźĻż╚żĘżŲAIź╣Ī╝źčĪ╝ź│ź¾źįźÕĪ╝ź┐ż╦╗╚ż©żļż└ż▒żŪżŽż╩ż»Ī󟻟ķź”ź╔źėźĖź═ź╣ż“╣įż”źŪĪ╝ź┐ź╗ź¾ź┐Ī╝żŪż╬╩┬š`▒ķōQĮĶ═²ż╩ż╔ż“╣ŌÅ]▓Įż╣żļ═ūĄßż╦żŌ▒■ż©żķżņżļżĶż”ż╦ż╩żļĪŻ╬╠ŠÅ│½╗ŽżŽ2023ŃQ¼Źż“═Į─ĻżĘżŲżżżļĪŻ

╗▓╣═½@╬┴

1. ĪųMicronĪó1β nmź╬Ī╝ź╔ż╬64Gźėź├ź╚ż╬DDR5x-DRAMż“źĄź¾źūźļĮą▓┘ĪūĪóź╗ź▀ź│ź¾ź▌Ī╝ź┐źļ (2022/11/08)

2. ĪųĪ┌Ų░▓ĶĪ█TSMCĖ”ē|〜▓±µ^Ė┬─ĻFree WebinarĪ╩9/28Ī╦ĪūĪóź╗ź▀ź│ź¾ź▌Ī╝ź┐źļ (2022/10/04)

3. "CeRAM: Correlated Electron Memory", KIT/Symerix International Symposium (2022/08/25)