IBMż╚┼ņ»Bź©źņź»ź╚źĒź¾ż¼Č”Ų▒│½╚»żĘż┐3D-ICź”ź¦Ī╝źŽź╣ź┐ź├ź»Č\Įč

IBM ResearchżŽĪó┼ņ»Bź©źņź»ź╚źĒź¾ż╚źčĪ╝ź╚ź╩Ī╝źĘź├źūż“±TżėĪóä▌ź╦źÕĪ╝źĶĪ╝ź»ä”ż╬źóźļźąź╦Ī╝ż╦ż¬żżżŲČ”Ų▒żŪ300mmź”ź¦Ī╝źŽŲ▒╗╬ż“└▄ŠÆż╣żļż┐żßż╬3D-ICź╣ź┐ź├ź»Č\Įčż“│½╚»żĘż┐ż╚źųźĒź░żŪ£½żķż½ż╦żĘż┐ĪŻ3D-ICżŽĪóTSVĪ╩through silicon viaĪ╦Č\ĮčżŪ2ĮŚ░╩æųż╬ź”ź¦Ī╝źŽŲ▒╗╬ż“└▄¶öżĘżŲ3╝ĪĖĄ┼¬ż╦ĮĖ└čż╣żļČ\ĮčĪŻŪ÷żżź”ź¦Ī╝źŽż“═Ų░ūż╦ŲDżĻ░Ęż©żļżĶż”ż╦żĘż┐ĪŻ

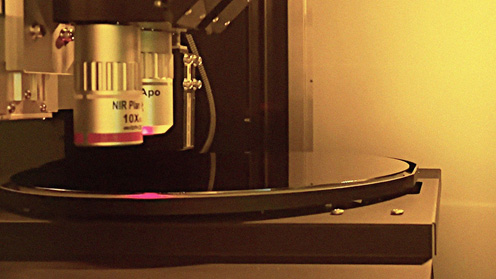

┐▐1ĪĪŪ÷żżź”ź¦Ī╝źŽż“═Ų░ūż╦ŲDżĻ░Ęż©żļżĶż”ż╦żĘż┐ĪĪĮąųZĪ¦IBM ResearchźųźĒź░

TSVżŽĪóź┴ź├źūŲ▒╗╬Ī╩ź”ź¦Ī╝źŽŲ▒╗╬Ī╦ż“─_ż═żŲŪ█└■ż“ż─ż╩ż░Č\ĮčżŪżóżļż¼ĪóŪ█└■š{(di©żo)▀`ż“ø]ż»ż╣żļż┐żßż╦╬óĀCż“Ū÷ż»║’ż├żŲżżżļĪŻżĮż╬Ė³żĄżŽ100µmż╦żŌ╦■ż┐ż╩żżĪŻÖ┌ŠÅ╣®µćżŪŪ÷ż»║’ż├żŲżĘż▐ż”ż╚Ī󟎟¾ź╔źĻź¾ź░ż¼žMżĘż»│õżņżõż╣ż»ż╩ż├żŲżĘż▐ż”ĪŻż│ż╬ż┐żßĪ󟣟џĻźóź”ź¦Ī╝źŽż╦└▄ŠÆżĄż╗żŲŲDżĻ░Ęż”ĪŻż│żņż▐żŪźŁźŃźĻźóź”ź¦Ī╝źŽżŽĪóźĘźĻź│ź¾ź”ź¦Ī╝źŽż“░Ęż”ż┐żßż╦ź¼źķź╣ź”ź¦Ī╝źŽż╦▐k╗■┼¬ż╦─źżĻ¤²ż▒żŲ╗╚ż├żŲżżż┐ĪŻź”ź¦Ī╝źŽĮĶ═²ż¼Į¬╬╗ż╣żļż╚Īó╚Ø│░└■źņĪ╝źČĪ╝ż“Š╚╝ożĘź¼źķź╣ż╚ź”ź¦Ī╝źŽż“│░żĘżŲżżż┐ĪŻ

źŁźŃźĻźóź”ź¦Ī╝źŽż╚żĘżŲźĘźĻź│ź¾ż“├ōżżżļŠņ╣ńżŌżóż├ż┐ż¼ĪóĄĪ│Ż┼¬ż╩╬üż“▓├ż©żŲ2ĮŚż╬ź”ź¦Ī╝źŽż“└┌żĻ▀`żĘżŲżżż┐ż┐żßĪó’L┤┘ż¼╚»Ö┌żĘ╩Ōé╬ż▐żĻż“─Ń▓╝żĄż╗żļĖČ░°ż╦ż╩ż├żŲżżż┐ĪŻ

żĮż│żŪĪóIBMż╚┼ņ»Bź©źņź»ź╚źĒź¾żŽĪó“£═Ķż╬ź¼źķź╣ź”ź¦Ī╝źŽż╦┬Õż’żĻ║YØŹ┼¬ż╩źĘźĻź│ź¾ź”ź¦Ī╝źŽż“├ōżżżŲżŌį~├▒ż╦2ĮŚż╬ź”ź¦Ī╝źŽż“╩¼▀`żŪżŁżļöĄ(sh©┤)╦Īż“Č”Ų▒│½╚»żĘż┐ĪŻźĘźĻź│ź¾ż╦żŽŲ®£½ż╩śĘ│░└■źņĪ╝źČĪ╝ż“╗╚ż├żŲĪó300mmź”ź¦Ī╝źŽż“╩¼▀`ż╣żļöĄ(sh©┤)╦Īż└ż╚żżż”ĪŻż│ż╬öĄ(sh©┤)╦Īż“╗╚ż©żąĪóäóÅøż╬Ė▀┤╣└Łżõ┐┐ȧź┴źŃź├ź»ż╬╠õ¼öż¼ż╩ż»ż╩żĻĪó’L┤┘ż“žōżķżĘĪó░█ż╩żļź”ź¦Ī╝źŽŲ▒╗╬ż╦┤žĘĖż╣żļźūźĒź╗ź╣æųż╬╠õ¼öżŌż╩ż»ż╩żļż╚żĘżŲżżżļĪŻ║Żövż╬Č\Į迎ĪóFOWLĪ╩Fan out wafer level packagingĪ╦żõ3Dź┴ź├źūźņź├ź╚ż╩ż╔ż╬└Ķ├╝źčź├ź▒Ī╝źĖČ\Įčż╦╗╚ż©żļČ\Įčż└ż╚żżż”ĪŻ

IBM ResearchżŽ2018ŃQ░╩═Ķ┼ņ»Bź©źņź»ź╚źĒź¾ż╚Č”Ų▒│½╚»żĘżŲżŁżŲż¬żĻĪóźņĪ╝źČĪ╝ż╦żĶżļź”ź¦Ī╝źŽ╩¼▀`Č\Įčż“┤░└«żĄż╗żļż│ż╚ż“ų`┼¬ż╚żĘżŲżŁż┐ĪŻ┐ʿʿżź┴ź├źū×æļ]ż╬ż┐żßż╦ØŁ═ūż╩×æļ]äóÅøż“│½╚»żĘżŲżŁż┐┼ņ»Bź©źņź»ź╚źĒź¾żŽĪó╬╠ŠÅĖ■ż▒300mm├ōż╬äóÅøż“└▀╝ŖżĘżŲżŁż┐ĪŻ║ŻĖÕżŽĪóż│ż╬źūźĒź╗ź╣ż¼╚ŠŲ│öüż╬µ£×æļ]╣®µćż╦╗╚ż©żļż│ż╚ż“╝┬Š┌żĘĪó3Dź┴ź├źūż╬ź╣ź┐ź├ź»ż“┐āż╣ż│ż╚ż╦ż╩żļĪŻ

╗▓╣═½@╬┴

1. "The breakthrough that could simplify the 3D chipmaking supply chain", IBM (2022/07/07)