TSMCż╬źŲź»ź╬źĒźĖĪ╝źĒĪ╝ź╔ź▐ź├źūĪ╩1Ī╦

TSMCż¼źŲź»ź╬źĒźĖĪ╝źĒĪ╝ź╔ź▐ź├źūż“2ĘŅż╬ISSCCĪ╩International Solid-State Circuits ConferenceĪ╦żŪ╚»╔ĮĪóŠ▄║┘ż╩ŲŌ═Ųż“Semiconductor Digest╗’ż¼ĘŪ║▄żĘżŲżżżļĪŻPete SingerįćĮĖ─╣ż╬ß×▓─ż“įużŲĪóż│ż│ż╦ĘŪ║▄ż╣żļĪŻ╣ų▒ķżĘż┐ż╬żŽTSMC▓±─╣ż╬Mark LiuĢ■żŪżóżļĪŻĄŁĄ£żŽżõżõ─╣żżż┐żßĪóØi╚Šż╚ĖÕ╚Š(╗▓╣═½@╬┴1)ż╦╩¼ż▒żļĪŻ

╔«ŪvĪ¦ Pete SingerĪóSemiconductor DigestįćĮĖ─╣

╚ŠŲ│öüźßĪ╝ź½Ī╝żŽĪóż│żņż▐żŪż╬ź╚źķź¾źĖź╣ź┐źņź┘źļżõź┴ź├źūźņź┘źļż╬źßźĻź├ź╚ż└ż▒żŪżŽż╩ż»ĪóźĘź╣źŲźÓźņź┘źļżŪż╬źßźĻź├ź╚ż“╝Ŗ▒Rż╣żļŠ}╦Īż“║╬├ōż╣żļØŁ═ūż¼żóżļĪóż╚LiuĢ■żŽĮęż┘ż┐ĪŻ╚ŠŲ│öüČ\Į迎Īóź╚źķź¾źĖź╣ź┐Č\Įčż╬▓■╬╔żõźßźŌźĻż╬┐╩·tĪóĖ·╬©┼¬ż╩┐«ęÄżõ┼┼Ė╗ż╬ČĪĄļĪó┐Ę║Ó╬┴ż╬│½╚»żõDTCOĪ╩└▀╝Ŗż╚źūźĒź╗ź╣ż╬Č©─┤║Ū┼¼▓ĮĪ╦Īó3╝ĪĖĄ╣Įļ]żžż╚╚»·tżĘĪóź╔źßźżź¾ź╣ź┌źĘźšźŻź├ź»ż╩Č\Įčż╦└┌żĻ╩¼ż▒Īóź┴ź├źūźņź├ź╚Č\Įčżõ└Ķ├╝źčź├ź▒Ī╝źĖź¾ź░Č\Įčż╚±Tżėż─ż»ż╬ż╦ż─żņĪóżŌż├ż╚ĮjżŁż╩▓┴├═ż“źµĪ╝źČĪ╝ż╦─¾ČĪżŪżŁżļżĶż”ż╦ż╩żļĪŻ

Īų┤╚ūČ\Įčż╚żĘżŲż╬╚ŠŲ│öüŠÅČ╚ż╬╠“│õżŽĪóż½ż─żŲż╩żżż█ż╔─_═ūż╦ż╩ż├żŲżżżļĪŻźŲź»ź╬źĒźĖĪ╝żŽż│żņż▐żŪż╬┐¶Ø▓ŃQ┤ųż╦┼ŽżĻĪóųMż┐ż┴ż╬╝ę▓±żõÖ┌īÖż╦─_═ūż╩╩č▓Įż“Ą┌ż▄żĘżŲżŁż┐ĪŻ└ż─cż╬┐═Ė²ż╬╚Š╩¼░╩æųż¼ź¬ź¾źķźżź¾żŪż─ż╩ż¼żĻĪó36▓»┐═ż╬SNSżõ26.3▓»┐═ż╬ź╣ź╚źĻĪ╝ź▀ź¾ź░źėźŪź¬ż“│┌żĘżßżļżĶż”ż╦ż╩ż├żŲżżżļĪŻż│ż”żżż├ż┐Ö┌īÖż“╩čż©ż┐źŲź»ź╬źĒźĖĪ╝┐╩·tż╬├µ┐┤żŽ£½żķż½ż╦╚ŠŲ│öüČ\ĮčżŪżóżļĪŻż█ż╚ż¾ż╔ż╬źżź╬ź┘Ī╝źĘźńź¾żŽ║Ū└Ķ├╝ź╬Ī╝ź╔ż╦Ų│Ų■żĄżņż┐ż¼Īóż│żņżŽ└Ķ├╝ź╬Ī╝ź╔Č\Įčż¼║ŪżŌ╣ŌÅ]żŪ╣Ōżżź©ź═źļź«Ī╝Ė·╬©ż“Ö┌ż▀ĮążĘż┐ż½żķż└Īūż╚LiuĢ■żŽĖņżļĪŻ

żĘż½żŌĪó║Ū└Ķ├╝ż╬źūźĒź╗ź╣ź╬Ī╝ź╔ż╬Č\Įčż¼ż│żņż▐żŪż╦ż╩ż»ĮjżŁż╩╣Łż¼żĻż“Ė½ż╗żŲżżżļĪŻż½ż─żŲżŽCPUżõFPGAż╩ż╔ż¼└Ķ├╝źŪźąźżź╣ż“╣Į└«żĘ├ō²ŗż¼Ė┬żķżņżŲżżż┐ż¼Īó7nmź╬Ī╝ź╔ż¼╚ŠŲ│öüż╬╬“╗╦ż╬├µżŪ╩¼┤¶┼└ż╚ż╩żĻĪó7nmźūźĒź╗ź╣ż╬▒■├ō×æē俎Īóź▐źżź»źĒźūźĒź╗ź├źĄż└ż▒żŪżŽż╩ż»5GżõGPUĪóź═ź├ź╚ź’Ī╝źŁź¾ź░Īóź▓Ī╝źÓĪóśOŲ░┘Zżžż╚╣Łż¼ż├żŲżżżļĪŻLiużŽĪóĪųTSMCż╬7nmČ\Įčż“╗╚ż├ż┐×æē俎150¹|╬Óż“«Ćż©Īó2020ŃQ8ĘŅ╗■┼└żŪż╣żŪż╦10▓»Ė─ż╬ź┴ź├źūż“Įą▓┘żĘż┐ż│ż╚ż╦ż╩żļĪŻż▐żĄż╦źŲź»ź╬źĒźĖĪ╝ż╬░c╝ń▓Įż╚żżż©żļĪūż╚Ė└ż”ĪŻ

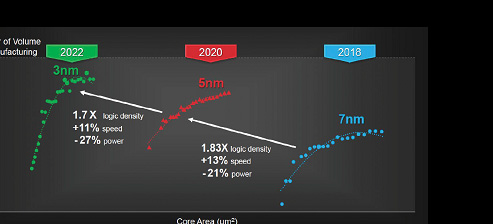

LiuĢ■żŽĪóźŲź»ź╬źĒźĖĪ╝ż¼ČÉŽ┬żĘżŲżŁż┐ż╚żżż”Ė½öĄż“╚▌─ĻżĘĪó│╬╝┬ż╦5nmĪó3nmżžż╚╚∙║┘▓ĮżŽ┐╩ż¾żŪżżżļż╚Ė└żżĪų3nmźūźĒź╗ź╣│½╚»żŽĮń─┤żŪĪóź╣ź▒źĖźÕĪ╝źļ─╠żĻż╦┐╩ż¾żŪżżżļĪūĪ╩┐▐1Ī╦ż╚Įęż┘żŲżżżļĪŻ

┐▐1ĪĪ└Ķ├╝źŲź»ź╬źĒźĖĪ╝ź╬Ī╝ź╔żŽ7nmż½żķ5nmĪó3nmżžż╚¶öż»ĪĪĮąųZĪ¦TSMC, Semiconductor Digest

ż│ż╬└ĶżŽĪóĮj│žż╚╠®└▄ż╦Č©╬üżĘĪó┐Ęź╚źķź¾źĖź╣ź┐╣Įļ]żõ┐Ę║Ó╬┴Īó┐ĘźóĪ╝źŁźŲź»ź┴źŃĪó3╝ĪĖĄĮĖ└čż“│½╚»żĘ3nm░╩æTż╬ź╬Ī╝ź╔ż╦īÖż½ż╣ż│ż╚ż“TSMCżŽ┴└ż├żŲżżżļĪŻ

║Ū└Ķ├╝ż╬7nmż╚5nmż╬źūźĒź╗ź╣żŪżŽĪó╝Īż╬żĶż”ż╩Č\Įčż“║╬żĻŲ■żņż┐ĪŻ

Ī”ź▓Ī╝ź╚└õ▒’╦ņż╬┼∙▓┴═Ų╬╠╦ņĖ³żõź╚źķź¾źĖź╣ź┐ż╬źšźŻź¾╔²ż╚Ę┴ėX

Ī”Ņ~Ų░┼┼╬«ż“æųż▓żļż┐żßż╬╣ŌöĪŲ░┼┘ź┴źŃź¾ź═źļ

Ī”║Ó╬┴ż╚źūźĒź╗ź╣ż╬ĮĖ└čĪ©Øi~├µ╣®µćżŪżŽ┤¾Ö┌═Ų╬╠Īó┤¾Ö┌°BŃ^ż“▓╝ż▓żļĪó

Ī”źūźĒź╗ź╣ĖÕ╣®µćĪ╩BEOLĪ╦żŪżŽĪóźąźĻźõĪ”Ū█└■ż╬▓■║¤Īó─Ńk═Č┼┼╬©║Ó╬┴ĪóCuźĻźšźĒĪ╝Īóźėźóż╩ż╔żŪ°BŃ^żõ═Ų╬╠ż“▓╝ż▓żļ

Ī”żĘżŁżż┼┼░Ąż╬╔į┼D╣ńż“║ŪŠ«ż╦ż╣żļż┐żßż╬ĖʿʿżźūźĒź╗ź╣öUĖµ

Ī”ź▓Ī╝ź╚ź╣ź┐ź├ź»╣Įļ]ż╬▓■║¤Ī©¾HżĘżŁżż┼┼░ĄĪ╩║ŪĮj7Ė─Ī╦żŪövŽ®źņź┘źļż╬┼┼╬üĪ”└Łē”ż“║Ū┼¼▓Į

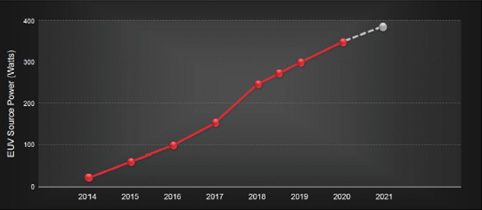

żĄżķż╦EUVźĻźĮź░źķźšźŻżŽĪóArFźĻźĮź░źķźšźŻż╬▓“ćĄ┼┘ż╬ź▄ź╚źļź═ź├ź»ż“▓“Š├żĘż┐─_═ūż╩źżź╬ź┘Ī╝źĘźńź¾żŪżóżļĪóż╚LiuĢ■żŽĮęż┘żŲżżżļĪŻEUVżŽźčź┐Ī╝ź¾ż╬├ķ╝┬┼┘ż¼╣Ōż»Ī󟥟żź»źļ╗■┤ųż¼ø]żżĪŻźūźĒź╗ź╣ż╬╩Ż╗©żĄż╚’L┤┘╠®┼┘ż“žōżķżĘż┐ĪŻEUVż╦żĶż├żŲĪó5nmź╬Ī╝ź╔żŪżŽź▐ź╣ź»┐¶ż“10ĮŚ░╩æųžōżķżĘż┐ż╚żżż”ĪŻØŖż╦Ū█└■ż╬└┌éāżõĪóź│ź¾ź┐ź»ź╚ĪóźėźóĪóźßź┐źļż╬źčź┐Ī╝ź╦ź¾ź░ż╦Ń~Ė·ż└ż├ż┐ż╚żĘżŲżżżļĪŻArFźĻźĮż╬ź▐źļź┴źčź┐Ī╝ź╦ź¾ź░ż╦×┤żĘżŲEUVżŽ1övż╬źčź┐Ī╝ź╦ź¾ź░żŪ║čż¾ż└ż┐żßż└ĪŻEUVĖ„Ė╗ż╬┐╩╩ŌżŌĮjżŁż»Ī╩┐▐2Ī╦Īó║Żżõ350Wż╦├ŻżĘżŲż¬żĻĪó5nmż╬╬╠ŠÅż“╝┬ĖĮżĘĪó3nmĪó2nmż╬│½╚»ż╦żŌ╠Oż“│½żżż┐ż╚Įęż┘żŲżżżļĪŻ

┐▐2ĪĪEUVĖ„Ė╗ż╬┐╩·tĪĪĮąųZĪ¦TSMCĪóSemiconductor Digest

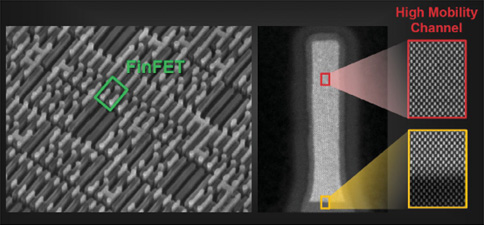

ź╚źķź¾źĖź╣ź┐╣Įļ]ż╚┐Ę║Ó╬┴ż╦żŌĖ└Ą┌żĘżŲż¬żĻĪó“£═Ķż╬Dennardż╬ź╣ź▒Ī╝źĻź¾ź░ō¦ż╚żŽ░ŃżżĪóźĒźĖź├ź»Č\Įčż¼żżżĒżżżĒż╩║Ó╬┴ż╚źŪźąźżź╣ż╬│ū┐ĘĪóövŽ®└▀╝Ŗż╬Č©─┤║Ū┼¼▓Įż“ŠW├ōż╣żļżĶż”ż╦ż╩ż├ż┐ĪŻ┐▐3ż╦żŽ╬╠ŠÅż╦żóżļ╣ŌöĪŲ░┼┘ź┴źŃź¾ź═źļż“ØŖ─╣ż╚ż╣żļ5nm FinFETź╚źķź¾źĖź╣ź┐ż“┐āżĘżŲżżżļĪŻ

┐▐3ĪĪ╣ŌöĪŲ░┼┘ź┴źŃź¾ź═źļż“Ęeż─FinFETĪĪĮąųZĪ¦TSMCĪóSemiconductor Digest

┐▐4ĪĪFinFETż“«Ćż©żŲź╩ź╬źĘĪ╝ź╚ź╚źķź¾źĖź╣ź┐żžĪĪĮąųZĪ¦TSMCĪóSemiconductor Digest

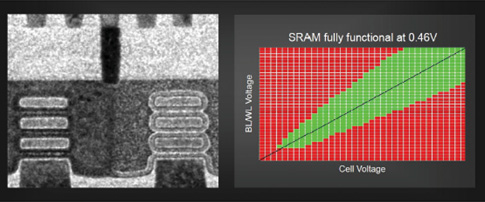

ż│ż╬└Ķż╬Fin FETż“«Ćż©żļź╚źķź¾źĖź╣ź┐╣Įļ]żŪżŽĪóź╩ź╬źĘĪ╝ź╚ź╚źķź¾źĖź╣ź┐ż¼└Łē”ż╚┼┼╬üĖ·╬©ż“▓■║¤ż╣żļż½żŌżĘżņż╩żżĪŻ┐▐4ż╬║ĖŖõż¼ź╩ź╬źĘĪ╝ź╚ź╚źķź¾źĖź╣ź┐ż╬TEMéāĀC└^┐┐żŪżóżļĪŻźĘĪ╝ź╚┤ųż╬╠®ż╩┤ų│ųżŪ┤¾Ö┌═Ų╬╠ż“žōżķżĘżŲżżżļż╚żżż”ĪŻż│ż╬ź╩ź╬źĘĪ╝ź╚ż“╗╚ż”ż│ż╚żŪź╔źņźżź¾┼┼░Ąż╦żĶż├żŲÖ┌żĖżļźąźĻźõ─Ń▓╝Ī╩drain induces barrier loweringĪ╦ż“╦╔ż«Ī󟥟ųź╣źņź├źĘźńźļź╔┼┼╬«ż╬’łżŁż“▓■║¤ż╣żļĪŻż│ż╬±T▓╠ĪóØiż╬└ż┬Õż╬ź╚źķź¾źĖź╣ź┐żĶżĻżŌ═źżņż┐övŽ®└Łē”ż“żŌż┐żķż╣żĶż”ż╦ż╩żļĪŻĪųź╚źķź¾źĖź╣ź┐└Łē”ż¼æųż¼żļż╚żżż”ż│ż╚żŽSRAMŲ░║Ņż╬VDDż“▓╝ż▓żķżņżļż│ż╚ż“┴T╠Żż╣żļĪūż╚LiuĢ■żŽĖņż├ż┐ĪŻ

╗▓╣═½@╬┴

1. TSMCż╬źŲź»ź╬źĒźĖĪ╝źĒĪ╝ź╔ź▐ź├źūĪ╩2Ī╦ (2021/05/21)