SPIźšź®Ī╝źķźÓĪų3╝ĪĖĄ╝┬äóżžż╬╠OĪūż¼┐āżĘż┐3D-ICż╬ĖĮ╝┬▓“

ź╗ź▀ź│ź¾ź▌Ī╝ź┐źļ╝ń╠¢ż╬SPIźšź®Ī╝źķźÓĪų3╝ĪĖĄ╝┬äóżžż╬╠OĪūż¼3ĘŅ25Ų³Īó│½╠¢żĄżņż┐(┐▐1)ĪŻ╣ŌĮĖ└č▓Įż╬Š}├╩ż“ż│żņż▐żŪż╬╚∙║┘▓Įż└ż▒żŪżŽż╩ż»Īóāeż╦└čż▀æųż▓żļöĄ╝░żŌ▓├ż’żļż╚Ė½żŲĪó┤ļ▓ĶżĘż┐ĪŻźĘź╣źŲźÓż½żķĖ½ż┐3DĪóźųĪ╝źÓż╦ż╩żĻżĮż”ż╩FO-WLPĪó╝┬║▌ż╦źßźŌźĻźĘź╣źŲźÓż“╣Į└«ż╣żļHMCĪóż╩ż╔ĖĮ╝┬▓“żŽŠÆ╝┬ż╦┐╩ż¾żŪżżżļĪŻ

┐▐1ĪĪSPIźšź®Ī╝źķźÓĪų3╝ĪĖĄ╝┬äóżžż╬╠OĪū╣ų▒ķ╔„Ę╩

║ŪĮķż╬╣ų▒ķżŽĪųźĘź╣źŲźÓźóĪ╝źŁźŲź»ź╚ż½żķĖ½ż┐3D-ICĪūż╚¼öżĘżŲĪóź╚źūź╣źĘź╣źŲźÓź║ż╬┬Õ╔ĮŲD─∙╠“żŪżóżĻĪóJEITAż╬3╝ĪĖĄĮĖ└čövŽ®źĄźųź│ź▀ź├źŲźŻ░čµ^żŪżŌżóżļŠŠ╦▄═┤ČĄĢ■ż½żķĪóźóźūźĻź▒Ī╝źĘźńź¾ż╚öU╠¾Š“°Pż╬╩č▓ĮżŪźóĪ╝źŁźŲź»ź┴źŃż¼ĮjżŁż»╩čż’żļĪóż╚żżż”ÅBż½żķ╗Žż▐ż├ż┐ĪŻ2000ŃQ┬Õż╦Ų■żĻĪóŠ├õJ┼┼╬üż╬öU╠¾ż½żķź▐źļź┴ź│źóĪóźßź╦Ī╝ź│źóżžż╚╩┬š`ĮĶ═²ż╦┐╩ż▀ĪóLSIżŌ└č┴ž▓Įż¼┐╩żÓż│ż╚żŽśO─śż└ż╚żĘż┐ĪŻ

┴╚ż▀╣■ż▀źĘź╣źŲźÓż╬ź│ź¾źįźÕĪ╝ź┐żŽżĄżķż╩żļ└Łē”żŌĄßżßżķżņżļĪŻ╬Ńż©żąĪ󟻟ļź▐ż╬▓ĶćĄŪ¦╝▒Ī”▓╗╠mŪ¦╝▒ż╦żŽ1TOPSĪ╩Tera Operations per SecondĪ╦░╩æųż╬└Łē”ż¼Ąßżßżķżņżļż╚żżż”ĪŻżĘż½żŌź╣ź▒Ī╝źķźėźĻźŲźŻż¼─_═ūżŪĪóź│źó┐¶ż“╗\żõżĘżŲżŌį~├▒ż╦└▀╝ŖżŪżŁżļŠ}╦Īż¼─_═ūż└ĪŻż▐ż┐CPUż╬└Łē”ż“æųż▓żļż”ż©żŪĪóCPUż╚źßźŌźĻż╚ż╬ż½żż▀`ż¼┐╩ż¾żŪżżżļĪŻ╬Ńż©żąĪóCPUż╬└Łē”żŽ╦ĶŃQ60%ż║ż─æųż¼ż├żŲżżżļż╬ż╦żŌż½ż½ż’żķż║ĪóźßźŌźĻż╬└Łē”żŽ╦ĶŃQ7%żĘż½╗\ż©żŲżżż╩żżĪŻżĮż│żŪĪóCPUż╬└Łē”ż“æųż▓żļż┐żßż╦╩┬š`└Łż“¾H├ōż╣żļĪŻ╠┐╬ßż╬Ų▒╗■╚»╣įż╚żżż”żĶż”ż╩╩┬š`▓Įż“╣įż”ĪŻ▐köĄĪóMOSź╚źķź¾źĖź╣ź┐żŽ╚∙║┘▓Įż╚Č”ż╦Īó╔nŲ»żĘż╩żżź╚źķź¾źĖź╣ź┐┐¶ż¼╗\ż©żļ’łĖ■ż¼żóżļĪŻż│ż╬ż┐żßĪóź▐źļź┴ź│źóżõźßź╦Ī╝ź│źóżŪŲ▒╗■ż╦Ų░ż½ż╣ź╚źķź¾źĖź╣ź┐┐¶ż“╗\żõżĘĪó╝■āS┐¶ż“æųż▓ż║ż╦ź»źĒź├ź»┼÷ż┐żĻż╬▒ķōQ┐¶ż“æųż▓żļĪŻ

żĮżņżŪżŌ└Łē”ż“żĄżķż╦æųż▓żļŠņ╣ńż╦żŽżõżŽżĻICź┴ź├źūż“└č┴žż╣żļż│ż╚ż╦ż╩żļĪŻż┐ż└żĘĪó╩Ōé╬ż▐żĻżĶż»ĪóżĘż½żŌį~├▒ż╦żżżĒżżżĒż╩ź┴ź├źūż“ż─ż╩ż▓żļżĶż”ż╦ż╣żļż┐żßż╦żŽĪó3D-ICż╬└▄¶öż“Č”─╠▓ĮżĘĪó3Dż╦żŽź┴ź├źūż“ŲDżĻ┤╣ż©żļż└ż▒żŪ║čżÓżĶż”ż╦ż╣żļż│ż╚ż¼─_═ūż╚żżż”ĪŻ

żĮż╬Øiż╦FO-WLPż¼└Ķ╣į

3D-ICż╦┐╩żÓØiż╦Īóź╣ź▐Ī╝ź╚źšź®ź¾ż╬żĶż”ż╩źŌźąźżźļźŪźąźżź╣żŪżŽĪóFO-WLPĪ╩Fan-Out Wafer Level PackagingĪ╦ż¼║ŻĖÕ╚»·tżĘżĮż”ż└ĪŻ║“ŃQ¼Źż╦│½╠¢żĄżņż┐ISSM 2014ż╬┤─┤╣ų▒ķżŪĪóTSMCż╬R&D Design and Technology Platformŗ╠ńż╬VPżŪżóżļCliff HouĢ■żŽĪóĪų3D-ICżŽż▐ż└└Ķż└ż¼ĪóInFOĪ╩Integrated Fan-OutĪ╦źčź├ź▒Ī╝źĖżŽ2015ŃQż╦ź╣ź┐Ī╝ź╚ż╣żļĪūż╚Įęż┘żŲżżż┐ĪŻTSMCż╬InFOż╚Ų▒══ż╩ź│ź¾ź╗źūź╚ż¼┼ņėøż╬£½ćŖ╝■įÆĢ■ż¼╣ų▒ķżĘż┐FO-WLPżŪżóżļ(┐▐2)ĪŻ

┐▐2ĪĪFO-WLPżŽźšźĻź├źūź┴ź├źūż“ÅøżŁ┤╣ż©żļ▓─ē”└Łż“╚ļżßżŲżżżļĪĪĮąųZĪ¦┼ņėø

£½ćŖĢ■żŽĪóFO-WLPżŽż▐ż║źŌźąźżźļ×æēäż╦╗╚ż’żņżļż└żĒż”ż╚Ė½żŲż¬żĻĪóżĮż╬═²Įyż“ĪóCPUż╚źóź╩źĒź░/RFż“1ź┴ź├źūż╦żĘż╦ż»żżż½żķż└ż╚ż╣żļĪŻźóź╩źĒź░/RFżŽ╚∙║┘▓ĮżĘż╦ż»żżż┐żßĪóźŪźĖź┐źļż╬CPUż╚ż╬1ź┴ź├źū▓ĮżŽžMżĘżżż╚ż╣żļĪŻCPUżŽĪó28nmż½żķ14/16nmżžż╚╚∙║┘▓Įż¼┐╩żÓ▐köĄżŪĪóźóź╩źĒź░/RFżŽ90nmż╚╚∙║┘▓Įż“┐╩żßżļż█ż╔żŪżŽż╩żżż½żķż└ĪŻźŌźąźżźļż╦żŽCPUż╚RF/źóź╩źĒź░ż¼’Lż½ż╗ż╩żżĪŻ2ź┴ź├źūż“┼ļ║▄ż╣żļż┐żßż╦żŽ“£═Ķż╬źšźĻź├źūź┴ź├źūż╩ż╔żŪżŽźżź¾ź┐Ī╝ź▌Ī╝źČż╬Ū█└■┴ž┐¶ż¼╗\ż©żŲżĘż▐ż”ż¼ĪóFO-WLPż└ż╚1┴žżŪ║čżÓż╚£½ćŖĢ■żŽĖ└ż”ĪŻ

3D-ICż╬║YØŹ▓Į║ŅČ╚żŌ┐╩·t

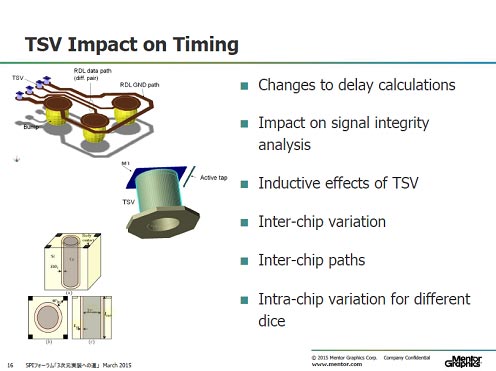

¶öżżżŲĪóĖĄźļź═źĄź╣ź©źņź»ź╚źĒź╦ź»ź╣żŪĖĮ║▀ĪóŠÅČ╚Č\Įč┴Ē╣ńĖ”ē|ĮĻż╬ćŖ╦▄└▓╔ūĢ■żŽSEMIż╬źčź├ź▒Ī╝źĖ║YØŹ▓Į░čµ^▓±ż╬źßź¾źąĪ╝ż╚żĘżŲĪó3D-ICż╬║YØŹ▓Į║÷─Ļ║ŅČ╚ż╦ż─żżżŲĮęż┘ż┐ĪŻTSVż╬├ōĖņż╬─Ļ▒Iż½żķ╗Žż▐żĻĪóTSVż╬╚┐żĻżõČ╩żĻż╩ż╔ż╬╝Ŗ▒RČ\Įčżõźóźķźżź¾źßź¾ź╚ź▐ź╣ź»ż╬░╠Åøż╩ż╔ż¼żóżļµć┼┘æä│╩ż¼»é─ĻżĘżŲż¬żĻĪ󟔟¦Ī╝źŽź╣ź┐ź├ź»ż╬Ų▒─Ļżõź▐Ī╝ź»Īóēää®╗Ņ┘xĪóź¼źķź╣źżź¾ź┐Ī╝ź▌Ī╝źČż╬æä│╩ż╩ż╔ż╦ż─żżżŲżŽ┐│Ą─├µż└ż╚żĘżŲżżżļĪŻ╬Ńż©żąĪó─_ż═╣ńż’ż╗ż┐ź┴ź├źūż╬Č╩ż▓╗Ņ┘xż╦┤žżĘżŲżŽĪóź½ź¾ź┴źņźąĪ╝ż╬żĶż”ż╦ź┴ź├źūż“ÅøżŁĪó╔wżżČ╩ż▓ź─Ī╝źļżŪ│õżņżļż▐żŪ╬üż“▓├ż©żļźŲź╣ź╚ż“─¾░ŲżĘżŲżżżļĪŻ

ĖßĖÕż½żķżŽĪóĖĮ║▀Īóź©źņź»ź╚źĒź╦ź»ź╣╝┬äó│ž▓±ć@═└Ė▄╠õż╬čŻ┼─╗@▐kĢ■ż¼Īó3D-ICż╬ź¬Ī╝źąĪ╝źėźÕĪ╝ż“╣įż├ż┐ĪŻ3D-ICż╩żķżŪżŽż╬źßźĻź├ź╚żŽĪóżõżŽżĻźßźŌźĻż╚źūźĒź╗ź├źĄż╬š{▀`ż“ø]ż»żĘĪóżĘż½żŌWide I/Oż╬żĶż”ż╦źóź»ź╗ź╣źėź├ź╚┐¶ż“512źėź├ź╚żõ1024źėź├ź╚ż╦╗\żõżĘ╩┬š`┼┘ż“æųż▓żŲĮĶ═²Å]┼┘ż“╔nż░▒■├ōż╦Ė■żżżŲżżżļż╚Įęż┘ż┐ĪŻGbps┼÷ż┐żĻż╬Š├õJ┼┼╬üĪóż╣ż╩ż’ż┴┼┼╬üĖ·╬©ż¼PoPż╬LPDDR3żĶżĻżŌ2.5Dż╬źżź¾ź┐Ī╝ź▌Ī╝źČż“╗╚ż”öĄż¼żĶżĻ─Ńż»Ī󿥿ķż╦3Dż╬TSVżŽżĄżķż╦┐¶╩¼ż╬▐kż╦žōżļż│ż╚ż“┐āżĘż┐ĪŻWide I/OżĶżĻżŌżĄżķż╦╩┬š`┼┘ż╬╣ŌżżHBMöĄ╝░ĪóHMCöĄ╝░ż╦ż─żżżŲżŌ┐©żņżŲżżżļĪŻż▐ż┐Īóźżź¾ź┐Ī╝ź▌Ī╝źČż“╗╚ż’ż║ż╦źūźĻź¾ź╚┤łæųż╬╚∙║┘Ū█└■ż“ŠW├ōżĘżŲĪóTSVź┴ź├źūż╚┬Šż╬ź┴ź├źūż“╩┬š`ż╦╩┬ż┘żŲŪ█Åøż╣żļ2.1Dż╦ż─żżżŲżŌĮęż┘żŲżżżļĪŻ

└▄¶öż╬ر═²ĖĪŠ┌ż╚└Łē”│╬Ū¦ż╬źĘź▀źÕźņĪ╝źĘźńź¾

źßź¾ź┐Ī╝ź░źķźšźŻź├ź»ź╣źĖźŃźčź¾ż╬Ńæ╗ęŽ┬ŪĘĢ■żŽĪóźżź¾ź┐Ī╝ź▌Ī╝źČż“ŠW├ōżĘżŲź┴ź├źūż“╩┬š`ż╦╩┬ż┘żļ2.5DöĄ╝░żŽĪó“£═Ķż╬└▀╝ŖČ\Įčż“╗╚ż©żļż│ż╚ż½żķĪó╚µ│ė┼¬─╣ż»¶öż»ż╬żŪżŽż╩żżż½ż╚Ė½żļĪŻż┐ż└żĘĪó3D-ICżžż╬ØŹ×óżŌÆÓżķż╩żżĪŻTSVż╦żĶżļź╣ź┐ź├ź»ICżŪżŽĪóź╣ź┐ź├ź»ż╣żļØiż╦ĘQ└▀╝ŖźŪĪ╝ź┐źšźĪźżźļ(GDS-II)ż“ż─ż╩ż«╣ńż’ż╗żŲر═²┼¬ż╩ĖĪŠ┌ż“╣įżżĪóŲ░║Ņż“│╬Ū¦ż╣żļĪŻżĮż╬ż┐żßż╬ź─Ī╝źļż¼CalibreżŪżóżļĪŻ

Calibre 3DSTACKĖĪŠ┌ź─Ī╝źļżŪżŽĪóĘQź┴ź├źūż╬└▄¶öŠ╩¾ż╬ĖĪŠ┌ż└ż▒żŪżŽż╩ż»ĪóŲ░║Ņź┐źżź▀ź¾ź░ż¼┤³┬į─╠żĻįużķżņżļż½ż╔ż”ż½ż╬ĖĪŠ┌żŌ╣įż”ĪŻ╬Ńż©żąź▐źżź»źĒźąź¾źūż¼▐kŗż└ż▒└▄¶öżĘżŲżżżŲżŌ╔į╬╔żŪżŽż╩żżż¼Īó░╠Åøż║żņż╦żĶżļ┤¾Ö┌═Ų╬╠ż╬╗\▓├ż╩ż╔żŪź┐źżź▀ź¾ź░ż¼ęÆżņż┐żĻĪóTSVż╬Ę┴ėXż╦żĶż├żŲ┤¾Ö┌źżź¾ź└ź»ź┐ź¾ź╣ż“Ö┌żĖż┐żĻż╣żļż│ż╚żŪź╬źżź║Ė╗ż╦ż╩ż├ż┐żĻĪóż│żņż▐żŪ╠õ¼öż╦ż╩ż├żŲżżż╩ż½ż├ż┐ż│ż╚ż¼╠õ¼öż╦ż╩żļż│ż╚ż¼żóżļĪŻCalibreżŽżĮżņż“ĖĪŠ┌ż╣żļ(┐▐3)ĪŻ▓├ż©żŲĪóÕXż╬╠õ¼öżŌĮążŲż»żļż┐żßĪóÕXż¼ż╔ż╬żĶż”ż╦Ų©ż▓żļż½ż“źĘź▀źÕźņĪ╝źĘźńź¾ż╣żļFloTHERMżŌ╗╚ż├żŲÕX╩¼╔█ż“Ė½└čżŌżļĪŻ

┐▐3ĪĪTSVż╬źĄźżź║żõ░╠Åøż╬ź║źņż¼ź┐źżź▀ź¾ź░ż╦▒ŲūxĪĪĮąųZĪ¦Mentor Graphics

źóź¾ź╔Ī╝źļźĘź╣źŲźÓźĄź▌Ī╝ź╚ż╬├½Ė²┘ćĮŃĢ■żŽĪóBGAźčź├ź▒Ī╝źĖżõźŽź¾ź└ź▄Ī╝źļż“╗╚ż├ż┐źčź├ź▒Ī╝źĖ├╝╗ęż¼┤łżõźżź¾ź┐Ī╝ź▌Ī╝źČż╚└▄¶öżĄżņżŲżżżļż½ż╔ż”ż½ż¼ż’ż½żķż╩żżĪóż╚żżż”╠õ¼öż“▓“»éż╣żļŠ}├╩ż╦ż─żżżŲĮęż┘ż┐ĪŻ3D-ICżõ┤łŲŌē┼ICż╩ż╔ż╬└▄¶öżŽĪóX└■ż“╗╚ż├żŲżŌ└▄¶öżĄżņżŲżżżļż½ż╔ż”ż½ż╬│╬Ū¦ćĶ╗Īż¼żŪżŁż╩żżĪŻżĮż│żŪĪóJTAG(źąź”ź¾ź└źĻź╣źŁźŃź¾)ż╚Ō}żążņżļźŲź╣ź╚╦ĪżŪ└▄¶öż“┼┼Ąż┼¬ż╦ź┴ź¦ź├ź»ż╣żļöĄ╦Īż“Šę▓żĘż┐ĪŻż│żņżŽĪóLSIŲŌŗż╬źčź├ź╔ŖZż»ż╦źąź”ź¾ź└źĻź╣źŁźŃź¾ź╗źļż╚öUĖµövŽ®ż“ĮĖ└čżĘżŲż¬ż»ØŁ═ūż¼żóżļż¼Īó└▄¶öŠ╩¾żŽź╗źļż“źĘźĻĪ╝ź║ż╦ź╣źŁźŃź¾ż╣żļż│ż╚żŪ╚ĮéāżŪżŁżļĪŻ

JTAGżĮż╬żŌż╬żŽż╣żŪż╦║YØŹ▓ĮżĄżņżŲżżżļż¼Īóż│żņż▐żŪżŽżóż▐żĻ╗╚ż’żņżŲż│ż╩ż½ż├ż┐ĪŻżĘż½żĘĪóBGAż╬╔ߥ┌ż╚Č”ż╦└▄¶öŠ╩¾ż“ź┴ź¦ź├ź»żĘż┐żĻĪ󟻟ņĪ╝źÓż╩ż╔żŪ╠ßż├żŲżŁż┐ź┴ź├źūż╬Ė╬ŠŃ▓“└Žż“żĘż┐żĻż╣żļż╬ż╦╔ߥ┌żĘżŲżŁż┐ż╚żżż”ĪŻ

źčź├ź▒Ī╝źĖź¾ź░ż╬Ö┌ŠÅ└Łż“æųż▓żļ

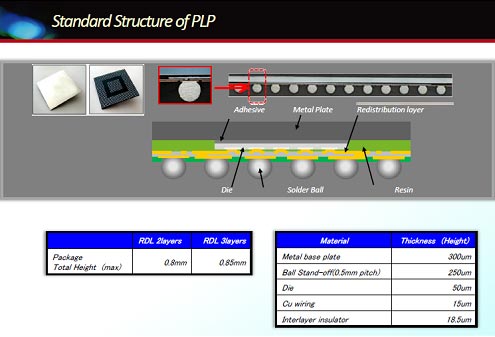

OSATż“┬Õ╔ĮżĘżŲĪóźĖź¦źżźŪźąźżź╣ż╬▒M╦¶ŠŽ╔ūĢ■żŽĪóźčź├ź▒Ī╝źĖż╬Ö┌ŠÅĖ·╬©ż“æųż▓żļż┐żßPLP (Panel Level Package)┤łż“ź┘Ī╝ź╣ż╦żĘż┐Č\Įčż“Šę▓żĘż┐ĪŻż│żņżŽĪóź└źżźĘź¾ź░żĘż┐Ė─╩╠ż╬ź┴ź├źūż“ź▐ź”ź¾ź╚Īóź▄ź¾źŪźŻź¾ź░ż╣żļż╬żŪżŽż╩ż»Īó50cm╗═öĄż╬ĮjżŁż╩┤łż╬æųż╬¾Hż»ż╬ź┴ź├źūż“źĻźšźĒĪ╝╝┬äóż╣żļżŌż╬ĪŻżĮż╬ĮjżŁżĄ(ĀC└č)żŽ300mmź”ź¦Ī╝źŽż╬3Ū▄żŌżóżļĪŻ

┐▐4ĪĪź┴ź├źūż╬╝┬äó┤łż“515mmĪ▀410mmż╬źčź═źļżŪźąź├ź┴ĮĶ═²ĪĪĮąųZĪ¦źĖź¦źżźŪźąźżź╣

żĮż╬éāĀCżŽ┐▐4ż╬żĶż”ż╦Īó║ŲŪ█└■żĄżņż┐źūźĻź¾ź╚┤łŲŌż╦ź┴ź├źūż“ļmżß╣■ż▀╝┬äóżĘĪ󿥿ķż╦æųż╦źßź┐źļźūźņĪ╝ź╚ż“╚’ż╗ż┐źčź═źļźĄźżź║ż╬┤łż½żķĪóźčź├ź▒Ī╝źĖźĄźżź║5mm│čż╬ICż└ż╚6752Ė─Īó10mm│čż╬ICżŪżŽ1652Ė─ĪóżĮżņżŠżņ▐k│ńżŪźčź├ź▒Ī╝źĖź¾ź░żŪżŁżļĪŻ

ĀC└čĪ”Š├õJ┼┼╬üż╬Ė·╬©żŽģsĘ▓ż╬HMC

║ŪĖÕż╦Īóź▐źżź»źĒź¾źĖźŃźčź¾ż╬─½┴ę║¤├ęĢ■żŽĪóTSVż“ŠW├ōżĘżŲ└čż▀─_ż═ż┐DRAMźßźŌźĻźóźņźżź┴ź├źūż“╣Į└«ż╣żļHMCĪ╩Hybrid Memory CubeĪ╦ż╦ż─żżżŲŠę▓żĘż┐ĪŻźūźĒź╗ź├źĄż╚ż│ż╬źßźŌźĻż“2.5Dżõ2.1Dż╬żĶż”ż╦Ū█ÅøżĘĪóźūźĒź╗ź├źĄż╬└Łē”ż“æųż▓żļĪŻHMCżŽĪó▌x╚╬ż╬DRAMż“ź╣ź┐ź├ź»żĘż┐żŌż╬żŪżŽż╩ż»Īó8Ė─ż╬DRAMźßźŌźĻźóźņźżż“ź╣ź┐ź├ź»żĘżŲżżżļĪŻ▐kż─ż╬ź┴ź├źūż╬źßźŌźĻźóźņźżż“16╩¼│õżĘżŲż¬żĻĪó╩¼│õżĄżņż┐ōļ░Ķż“ź▄Ī╝źļź╚Ī╩VaultĪ╦ż╚Ō}żėĪóźßźŌźĻż╬ź▄Ī╝źļź╚ż“āeż╦8ĮŚ╩¼Č·╗╔żĘż╦żĘżŲżżżļĪŻźßźŌźĻżŽź▄Ī╝źļź╚ż┤ż╚ż╦źóź»ź╗ź╣ż╣żļĪŻźßźŌźĻźŁźÕĪ╝źųż╦żŽ16Ė─ż╬ź▄Ī╝źļź╚ōļ░Ķż¼żóżĻĪóżĮżņżŠżņżŽŲ╚╬®żĘżŲżżżļ(┐▐5)ĪŻ

┐▐5ĪĪHMCż╬ź│ź¾ź╗źūź╚ĪĪĮąųZĪ¦Micron Technology

8ĮŚż╬źßźŌźĻż“öUĖµż╣żļż╬żŽ║Ū▓╝┴žż╬źĒźĖź├ź»żŪżóżļĪŻż│ż│żŪżŽĪóBSTĪ╩Built-in Self-TestĪ╦ĪóĖĒżĻĖĪĮąĪ”ÖÄ┘ćĪóź▄Ī╝źļź╚ŲŌżŪż╬źĻź┌źóż╩ż╔ż“╣įż”ĪŻżĄżķż╦Īóż│ż╬źĒźĖź├ź»ź┴ź├źūż╦żŽĪóźßźŌźĻż╚źūźĒź╗ź├źĄźĻź¾ź»ż╚ż“ż─ż╩ż░źĻź¾ź»źżź¾ź┐źšź¦Ī╝ź╣öUĖµövŽ®ż¼żóżĻĪóźūźĒź╗ź├źĄż╚─╠┐«ż╣żļĪŻ

║Żövż╬ŗī2└ż┬Õż╬HMCżŪżŽĪó4╦▄ż╬źĻź¾ź»ż“×óż©ĪóżĮżņżŠżņż╬źĻź¾ź»ż┤ż╚ż╦£pż▒ż╚┴„żĻżŪżĮżņżŠżņ║ŪĮj16źņĪ╝ź¾ż“Ęeż─ĪŻĘQźņĪ╝ź¾żŽ10GbpsżŪŲ░ż»ż┐żßĪó1źņĪ╝ź¾µ£öüżŪżŽ320GbpsĪĪĪß40GB/sż╚ż╩żĻĪóµ£ŗżŪ4źņĪ╝ź¾żóżļż┐żß160GB/sż╚ż╩żļĪŻHMC║ŪĮjż╬źßźĻź├ź╚żŽź▄Ī╝ź╔ź╣ź┌Ī╝ź╣ż¼“£═Ķż╬DRAMż╚╚µż┘1/10ż╦žōżĻĪóŠ├õJ┼┼╬üżŌĮjżŁż»žōŠ»ż╣żļż│ż╚ĪŻ╬Ńż©żąDDR3żŪ╣Į└«ż╣żļż╚2.25kWż└ż├ż┐ż╬ż¼ĪóHMCżŪżŽ330Wż╦žōż├ż┐ĪŻ

HMCżŽĪ󟎟żź©ź¾ź╔ż╬HPCĪ╩High Performance ComputingĪ╦żõ─╠┐«ź═ź├ź╚ź’Ī╝ź»ż╬┤├ŽČ╔ĪóźŪĪ╝ź┐ź╗ź¾ź┐Ī╝ż╬źĄĪ╝źąĪ╝ż╩ż╔ĪóźūźĒź╗ź├źĄż╬Å]┼┘ż“Ēöż”źŽźżź©ź¾ź╔╩¼╠ŅżŪ╗╚ż’żņżļż└żĒż”ĪŻ