EIDECĪóź░źĒĪ╝źąźļČ©╬üżŪ10nm±śż╬▓├╣®ż╦EUVŲ│Ų■ų`╗žż╣Ī╩3Ī╦Ī┴źņźĖź╣ź╚

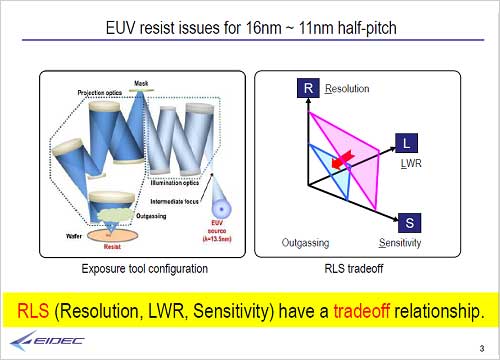

źšź®ź╚źņźĖź╣ź╚żŪżŽĪó║“ŃQż▐żŪżŽź▌źĖĘ┐źņźĖź╣ź╚ż“╗╚żżĪó▓“ćĄ┼┘16nm░╩▓╝ĪóLWRĪ╩└■╔²ż╬»¤żĄĪ¦line width roughnessĪ╦1.3nm░╩▓╝Īó┤Č┼┘10mJ/cm2░╩▓╝Īóż╚żżż”┐¶├═ż“įużŲżżż┐ĪŻ▓“ćĄ┼┘ż╚LWRĪó┤Č┼┘ż╬įÆż─ż╬źčźķźßĪ╝ź┐żŽź╚źņĪ╝ź╔ź¬źšż╬┤žĘĖż╦żóżļż┐żßĪóįÆż─ż╬źčźķźßĪ╝ź┐ż“║Ū┼¼▓ĮżĄż╗żļØŁ═ūż¼żóżļ(┐▐8)ĪŻ║ŻŃQżŽĪóź═ź¼Ę┐źņźĖź╣ź╚ż“╗╚ż├żŲż╔ż│ż▐żŪżżż▒żļż½ż╬╝┬┘xżŪżóżļĪŻ

┐▐8ĪĪźņźĖź╣ź╚ż╬ź╚źņĪ╝ź╔ź¬źšĪĪĮąųZĪ¦EIDEC

ź═ź¼Ę┐źņźĖź╣ź╚żŪżŽĪóźčź┐Ī╝ź¾ż¼╩°żņżļż╚żżż”╠õ¼öż¼ÅŚżŁż┐ĪŻż╔ż”żõżķĖČ░°żŽ┤łż╚ż╬╠®ŠÆ└Łż¼ĒśżĘżżż│ż╚ż└ż├ż┐ĪŻż│ż╬ż┐żßż▐ż║żŽ▓╝├Žż╚ż╬╠®ŠÆ└Łż“æųż▓ż┐ĪŻź╚ź├źūźŪĪ╝ź┐ż╚żĘżŲżŽL/Sż╚żĘżŲ18nmż¼įużķżņżŲżżżļĪŻ

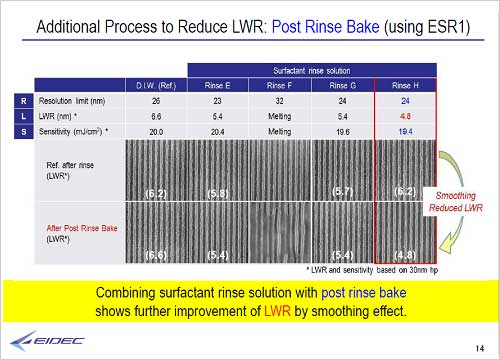

╝Īż╦ĪóĖĮćĄĖÕż╬źĻź¾ź╣╣®µćż“Ė½─ŠżĘż┐ĪŻŽ¬Ė„ó¬ź┘Ī╝ź»ó¬ĖĮćĄó¬źĻź¾ź╣ó¬ė|┴ńĪóż╚żżż”▐kŽóż╬źšź®ź╚źĻźĮ╣®µćż╬║ŪĖÕż╬źĻź¾ź╣╣®µćż╦ÅRų`żĘż┐ĪŻż│ż│żŪżŽĪóĮŃ┐Õż└ż▒żŪżŽż╩ż»─cĀCīÖ└Ł║▐ż╬Ų│Ų■żŌ╗Ņż▀ż┐ĪŻżĄżķż╦źĻź¾ź╣ż╚┤Č„[ż╚ż╬┤ųż╦Īóź┘Ī╝ź»╣®µćż“Ų■żņżļż╚LWRżŽ▓■║¤żĄżņż┐ĪŻ╝┬┘xżŪżŽLWRż¼6.2nmż└ż├ż┐ż╬ż¼4.8nmż╦žōŠ»żĘż┐(┐▐9)ĪŻ

┐▐9ĪĪźĻź¾ź╣ĖÕż╬ź┘Ī╝ź»ż╦żĶż├żŲLWRż“žōżķżĘż┐ĪĪĮąųZĪ¦EIDEC

żĄżķż╦LWRż“žōżķż╣ż┐żßż╦ĪóźņźĖź╣ź╚ż╬źčź┐Ī╝ź¾ż¼ż╔ż╬żĶż”ż╦ĖĮ楿╦żĶż├żŲ═Žż▒żŲżżż»ż½ż“AFMĪ╩atomic force microscopeĪ╦ż“╗╚ż├żŲ─┤ż┘ż┐ĪŻAFMżŽ║┘żż┐╦ż╚╗Ņ╬┴╔ĮĀCż╚ż╬ĖČ╗ę┤ų╬üż“▐k─Ļż╦żĘż╩ż¼żķĪó╗Ņ╬┴╔ĮĀCż“żĮż╬┐╦żŪż╩żŠżļż│ż╚żŪ▒·õüż“źėźĖźÕźóźļ▓Įż╣żļŠ}╦ĪżŪżóżļż¼ĪóĖĮćĄķ]├µżŪ┐╦ż“╣ŌÅ]ż╦┐ČŲ░żĄż╗ż╩ż¼żķź╣źŁźŃź¾żĘż┐ĪŻ╗Ņ╬┴ż╚┐╦ż╚ż╬┤ųż╦żŽĖĮćĄķ]ż“ÅRŲ■Ī󿥿ķż╦ĮŃ┐Õż“ÅRŲ■żĘżŲźĻź¾ź╣ż╣żļż│ż╚żŪķWżżżŲ╣įż»ĪŻźņźĖź╣ź╚ż¼┤ČĖ„żĘĪóĖĮćĄķ]ż╦═Žż▒ż╩żż╩▌ĖŅ┤ż¼ż╔ż”║Ņ├ōż╣żļż╬ż½Īóż│ż╬źßź½ź╦ź║źÓż“żŁż┴ż¾ż╚═²▓“żŪżŁżņżąLWRż“žōżķż╣ż│ż╚ż¼żŪżŁżļż╚Ė½żŲżżżļĪŻAFMż“ŠW├ōż╣żļŠ}╦ĪżŽSelete╗■┬Õż╦│½╚»żĄżņż┐żŌż╬ż└ż╚żżż”ĪŻ

źņźĖź╣ź╚ż½żķż╬źóź”ź╚ź¼ź╣żŽ10ŃQØiż½żķ╠õ¼öż¼ĮążŲżżż┐ż╚żżż”ĪŻSelete╗■┬ÕżŽź¼ź╣┴ĻżŪ┬¬ż©żĶż”ż╚żĘżŲĪóź¼ź╣ź»źĒź▐ź╚ź░źķźšźŻżŪ╩¼└ŽżĘżŲżżż┐ĪŻżĘż½żĘĪóASMLżŽĪóź¼ź╣ż¼╚»Ö┌żĘżŲĄ█ŠÆżĄżņżŲżŌźŪźąźżź╣ż╦ĄK▒Ųūxż“Ą┌ż▄ż╣ż╬ż└żĒż”ż½Īóż╚żżż”Ą┐╠õż“─ĶżĘż┐ż╚żżż”ĪŻż│ż╬ż┐żßż╦żŽźóź”ź╚ź¼ź╣ż“─Š└▄ćĶ▒Rż╣żļØŁ═ūż¼żóżļĪŻżĄżŌż╩ż▒żņżąźŪźąźżź╣źßĪ╝ź½Ī╝ż╦╩▌Š┌żŪżŁż╩ż»ż╩żļĪŻ

ż│żņż▐żŪASMLżŽĪó┼┼╗ęźėĪ╝źÓż“źņźĖź╣ź╚źšźŻźļźÓż╦Š╚╝ożĘżŲźóź”ź╚ź¼ź╣ż╦żĶżļź│ź¾ź┐ź▀ź═Ī╝źĘźńź¾╦ņż¼żŪżŁżļż╚żĘżŲĪóżĮżņż“ź©źĻźūźĮźßĪ╝ź┐żŪ╦ņĖ³ż“▒Rżļż│ż╚żŪźóź”ź╚ź¼ź╣ż╬╬╠ż“Ė½└čżŌż├żŲżżż┐ĪŻżĄżķż╦H2źķźĖź½źļż╦żĶż├żŲź½Ī╝ź▄ź¾ż╦▒°ģ¢żĄżņż┐╦ņż“¹ÉŠ¶żĘż┐ĖÕĪóXPSż╦żĶż├żŲ└«╩¼ż“╩¼└Žż╣żļ(┐▐10ż╬║Ėæų)ĪŻ

┐▐10ĪĪźóź”ź╚ź¼ź╣äh▓┴╦Īż╬ĖĪŲż╗Žż▐żļĪĪĮąųZĪ¦EIDEC

ż┐ż└żĘĪó┼┼╗ęźėĪ╝źÓż“Š╚╝oż╣żļż│ż╚żŪ╝┬▌åż“╔ĮżĘżŲżżżļż╚żżż©żļż└żĒż”ż½Īóż╚EIDECżŽĄ┐╠õż“┼Ļż▓ż½ż▒Īóäh▓┴Š}╦Īż“│╬╬®żĘżĶż”ż╚żĘż┐ĪŻEIDECżŽ┼┼╗ęźėĪ╝źÓżŪżŽż╩ż»EUVĖ„ż“─Š└▄┼÷żŲżļż│ż╚żŪĪóźóź”ź╚ź¼ź╣ż¼╚»Ö┌ż╣żļż╚╣═ż©żŲżżżļ(┐▐10ż╬║Ė▓╝)ĪŻżõżŽżĻź│ź¾ź┐ź▀╦ņż╬Ė³żĄ▒R─ĻĪóH2źķźĖź½źļ¹ÉŠ¶ĪóXPS╩¼└Žż╚Ų▒══ż╦╣įż”öĄ╦Īż“┐╩żßżŲżżżļĪŻ┤┴├źŪĪ╝ź┐ż¼ĮĖż▐żĻż─ż─żóżļĪŻ

║ŻŃQż╬4ĘŅż½żķ╗Žż▐ż├ż┐DSAżŽĪóż│żņż½żķ╦▄│╩┼¬ż╦╝{ĄßżĘżŲżżż»źūźĒźĖź¦ź»ź╚żŪżóżļż¼ĪóEIDECżŪ░Ęż”źŲĪ╝ź▐ż╚ż╩ż├ż┐ż╬żŽĪóźĻźĮź░źķźšźŻż╚żŽŲ╚╬®ż╦╚∙║┘źčź┐Ī╝ź¾ż“║Ņżļż│ż╚ż¼żŪżŁżļČ\Įčż╬▐kż─ż└ż½żķżŪżóżļĪŻżĮżņżŌź¼źżź╔źčź┐Ī╝ź¾ż“Ę┴└«żĘżŲż¬żŁĪóź▌źĻź▐Ī╝ż¼żĮżņż╦▐pż├żŲśOŲ░┼¬ż╦źóź╗ź¾źųźĻż╣żļż╚żżż”Č\Įčż└(┐▐11)ĪŻEUVż╚DSAżŽ┴Ļ▌öż”ż│ż╚żŪ╚∙║┘▓Įż¼▓─ē”ż╦ż╩żļĪŻEUVźĻźĮź░źķźšźŻżŽASML1╝ężĘż½źūźņźżźõĪ╝żŽżżż╩żżż┐żßĪó║Ó╬┴ż└ż▒żŪźčź┐Ī╝ź╦ź¾ź░Įą═ĶżļČ\Įčż“Ų³╦▄ż¼▓ĪżĄż©żŲż¬ż»ż┘żŁż└ż╚żżż”┴TĖ½żŌ║¼äėżżĪŻ

┐▐11ĪĪEUVż╚DSAż╬╬ŠöĄżŪ10nm╠ż╦■ż╬źčź┐Ī╝ź¾ż“▓├╣®ż╣żļĪĪĮąųZĪ¦EIDEC

ź│ź¾ź┐ź»ź╚żõź╣źļĪ╝ź█Ī╝źļż╬źčź┐Ī╝ź¾ż╦DSAż╬╦ņż“¤²ż▒ÕXĮĶ═²ż╣żļż╚╦ņżŽĮ╠Š«ż╣żļż┐żßĪóLWRżŽ─Ńžōż╣żļż└żĒż”ż╚żĘżŲżżżļĪŻźĄźų10nmż╬L/Sż“┴└żżĪó║Ó╬┴│½╚»ĪóØó╦Ī╝Ŗ▒RČ\ĮčĪóźĘź▀źÕźņĪ╝źĘźńź¾ĪóŪ█└■ż╬ź¬Ī╝źūź¾Ī”źĘźńĪ╝ź╚ĖĪØhż▐żŪ╣įż”╝Ŗ▓Ķż└ĪŻ

EUV│½╚»żŪżŽĪóŽ¬Ė„ĄĪżŽASMLż╚IMECĪóź▐ź╣ź»żõźņźĖź╣ź╚ż╬╠õ¼öżŽEIDECż╚SEMATECHż╚ĪóŲ³▓żä▌ż╬3├Ž░Ķż¼Č”Ų▒żĘżŲŲDżĻ┴╚żÓźŲĪ╝ź▐ż╚ż╩ż├ż┐ĪŻż│ż╬╣±║▌ź│źķź▄źņĪ╝źĘźńź¾żĮż╬żŌż╬żŌĪóżĮż╬├µ┐┤ż╦ź│ź¾źĮĪ╝źĘźóźÓż¼3ŪvŲ■ż├żŲżżżļż╬żŌĪóĮķżßżŲż╬└ż─c┼¬ż╩ź│źķź▄źņĪ╝źĘźńź¾ż╬╗Ņż▀żŪżóżļĪŻ└«Ė∙żĄż╗ż┐ČŪż╦żŽŲ³╦▄żŽ║Ų┼┘Īó└ż─cźņź┘źļż╬×æļ]╬üż“┐āż╣ż│ż╚ż¼żŪżŁżļż└żĒż”ĪŻ

Ī╩ż│ż╬źĘźĻĪ╝ź║Į¬╬╗Ī╦

╗▓╣═½@╬┴

1. EUV╗■┬Õż¼Ė½ż©żŲżŁż┐ż½ĪóIntelż¼ASMLż╚╩Ō─┤ż“╣ńż’ż╗10nmż╦Š╚ØŹ (2013/05/22)

2. EIDECĪóź░źĒĪ╝źąźļČ©╬üżŪ10nm±śż╬▓├╣®ż╦EUVŲ│Ų■ų`╗žż╣Ī╩1Ī╦Ī┴▄ć═ū (2013/05/31)

2. EIDECĪóź░źĒĪ╝źąźļČ©╬üżŪ10nm±śż╬▓├╣®ż╦EUVŲ│Ų■ų`╗žż╣Ī╩2Ī╦Ī┴ź▐ź╣ź»ĖĪØh (2013/05/31)