TSMCĪóŃ~ĄĪźżź¾ź┐Ī╝ź▌Ī╝źČż╦żĶżļCoWoSČ\Įčż╬═ź░╠└Łż“╝┬Š┌

└Ķ├╝źčź├ź▒Ī╝źĖĪ╩Advanced PackageĪ╦Č\Įčż¼║ŻĖÕICźčź├ź▒Ī╝źĖż╬├µżŪ║ŪżŌĮj(lu©░)żŁż╩└«─╣ż“ā~ż▓żļż╚▌xŠņ─┤Øh▓±╝ęż¼═Į▒RżĘżŲżżżļ─╠żĻĪóAppleż╬źčźĮź│ź¾├ōźūźĒź╗ź├źĄżŪżóżļM1ź┴ź├źūżõNvidiaż╬║Ū┐ĘGPUź┴ź├źūH100Ī╩┐▐1Ī╦ż╩ż╔ż╦╗╚ż’żņżŲżżżļĪ╩╗▓╣═½@╬┴1Ī╦ĪŻż│ż│żŪżŽźżź¾ź┐Ī╝ź▌Ī╝źČČ\Įčż¼ź½ź«ż“É█(©żi)żļĪŻTSMCżŽŃ~ĄĪźżź¾ź┐Ī╝ź▌Ī╝źČż╦żĶżļCoWoSČ\Įčż¼└Łē”ż└ż▒żŪżŽż╩ż»┐«═Ļ└ŁżŌ═źżņżŲżżżļż│ż╚ż“£½żķż½ż╦żĘż┐ĪŻ

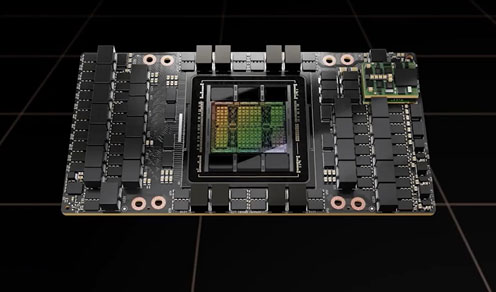

┐▐1ĪĪNvidiaż╬║Ū┐ĘGPUĪųH100Īūż“┼ļ║▄żĘż┐ź▄Ī╝ź╔ĪĪĮąųZĪ¦Nvidia

└Ķ├╝źčź├ź▒Ī╝źĖČ\Į迎2.5DżóżļżżżŽ3D-ICż╩ż╔ż╚Ō}żążņżŲżżżļż¼ĪóżĮż╬└ż─c▌xŠņżŽ2020ŃQż½żķ2027ŃQż╦ż½ż▒żŲŃQ╩┐Čč└«─╣╬©CAGRż¼10.2%żŪ└«─╣ż╣żļż╚żżż”═Į▒Rż½żķĪó7.84%└«─╣żõ8%└«─╣ż╩ż╔żżżĒżżżĒż╩▌xŠņ─┤Øh▓±╝ęż½żķ╚»╔ĮżĄżņżŲżżżļĪŻ▌xŠņæä╠ŽżŌ2026ŃQż╦382▓»ź╔źļżõ475▓»ź╔źļĪó2027ŃQż╦642▓»ź╔źļĪó2028ŃQż╦550▓»ź╔źļż╩ż╔▌xŠņ─┤Øh▓±╝ęż╦żĶż├żŲż▐ż┴ż▐ż┴żŪżóżļĪŻż╚żŽżżż©Īó400Ī┴500▓»ź╔źļż╦└«─╣ż╣żļż╚ż▀żŲżĶżżż└żĒż”ĪŻ

ż╩ż╝ż½ĪŻTSMCżŽ╚∙║┘▓Įż╬└ĶŲ¼ż“└┌ż├żŲĪó7nmĪó5nmż╚żõż├żŲżŁżŲ║ŪŖZżŪżŽ4nmż╚╚∙║┘▓Įż“┐╩żßżŲżżżļż¼Īóź│ź╣ź╚┼¬ż╦żŽČ╦żßżŲ╣Ōż»ż╩ż├żŲżżżļĪŻ╬Ńż©żąĪóTSMCżŽ7nm░╩▓╝ż╬ź”ź¦Ī╝źŽż“µ£┼ĻŲ■ź”ź¦Ī╝źŽż╬1Ī┴2│õżĘż½žéżßżŲżżż╩żżż¼ĪóżĮż╬Ūõæų±YżŽµ£öüż╬╚Š╩¼ż╦żŌĄ┌żųĪŻź│ź╣ź╚ż¼ż½ż½żļż┐żß×æļ]źĄĪ╝źėź╣▓┴│╩żŌæųż▓żŲżżżļĪŻż│ż╬ż┐żßĪóĄĮj(lu©░)ż╩ź┴ź├źūżĶżĻżŽövŽ®ż┤ż╚ż╦Š«żĄż╩ź┴ź├źūźņź├ź╚ż╦╩¼│õżĘżŲ└┌żĻĮążĘĪóź▐źļź┴ź┴ź├źū╝┬äóż╣żļöĄ(sh©┤)ż¼ŖWżżĪóż╚Ų▒╝ęDirectorżŪżóżļShin-Puu JengĢ■(hu©¼)żŽĖ└ż├żŲżżżļĪŻż│ż╬ź▐źļź┴ź┴ź├źūźčź├ź▒Ī╝źĖż¼└Ķ├╝źčź├ź▒Ī╝źĖżŪżóżļĪŻ

ż┐ż└żĘź┴ź├źūźņź├ź╚żõźßźŌźĻĪóSerDesż╩ż╔ż╬╝■╩šövŽ®ż╬źūźĒź╗ź╣ź╬Ī╝ź╔żŽż▐ż┴ż▐ż┴żŪĪóżĘż½żŌŪ█└■ż╬┼┼Č╦źčź├ź╔żŌźąźķźąźķż╩ż╬żŪĪóŪ█└■ż“żĘ─ŠżĄż╩ż▒żņżąźčź├ź▒Ī╝źĖź¾ź░żŪżŁż╩żżĪŻżĮż│żŪ║ŲŪ█└■┴žĪ╩Redistribution LayerĪ╦ż╚ż╩żļźżź¾ź┐Ī╝ź▌Ī╝źČż“Ų│Ų■żĘżŲ║ŪĮ¬┼¬ż╦źūźĻź¾ź╚┤łż╦╝┬äóżĘżõż╣ż»ż╣żļĪóżóżļżżżŽ║YØŹ┼¬ż╩źįź¾Ū█Åøż╦╣ńż’ż╗żļż╬żŪżóżļĪŻ

źĘźĻź│ź¾æųż╦övŽ®ż“╣Į└«żĘż┐ź└źżżŽĪóźżź¾ź┐Ī╝ź▌Ī╝źČæųż╦├╝╗ęż“ź▄ź¾źŪźŻź¾ź░żĄżņĪóźżź¾ź┐Ī╝ź▌Ī╝źČŲŌż╬║ŲŪ█└■┴žż“─╠żĻĪóźūźĻź¾ź╚övŽ®┤łĪ╩źĄźųź╣ź╚źņĪ╝ź╚Ī╦ż╬┼┼Č╦źčź├ź╔ż╚└▄¶öżĄżņżļĪŻĮj(lu©░)żŁż╩źĘźĻź│ź¾ź└źżż└ż╚╩Ōé╬ż▐żĻż¼ĄKżżż¼ĪóŠ«żĄż╩źĘźĻź│ź¾ż╦╩¼│õż╣żļöĄ(sh©┤)ż¼żŌżŽżõź│ź╣ź╚ż¼ŖWż»ż╩żļĪóż╚TSMCż╬JengĢ■(hu©¼)żŽĖ└ż”ĪŻ▓├ż©żŲ╚┐żĻż¼žō(f©┤)Š»żĘĪó┐«═Ļ└ŁżŌ╣Ōż▐żļż╚żĘżŲżżżļĪŻźżź¾ź┐Ī╝ź▌Ī╝źČśO┐╚ż╬Įj(lu©░)żŁżĄżŽźņź┴ź»źļźĄźżź║Ī╩32mmĪ▀26mmĪ╦ż“┤╦▄├▒░╠ż╚ż╣żļĪŻ

ż│ż╬źżź¾ź┐Ī╝ź▌Ī╝źČż╬║Ó╬┴ż╚żĘżŲżŽźĘźĻź│ź¾ź”ź¦Ī╝źŽż“╗╚ż”Š}ż¼ż│żņż▐żŪżŽŃ~Ė·ż└ż├ż┐ĪŻżżż’żµżļźĘźĻź│ź¾źżź¾ź┐Ī╝ź▌Ī╝źČżŪżóżļĪŻżĘż½żĘĪóTSVĪ╩Through Silicon ViaĪ╦ż¼┐╝ż»ż╩żĻż╣ż«żļż╚Ū█└■┴žż¼╝┬ä®┼¬ż╦─╣ż»ż╩żļĪŻŪ█└■ż¼─╣ż»ż╩żļż╚źŪĪ╝ź┐Å]┼┘ż¼═Ņż┴żļż└ż▒żŪżŽż╩ż»ĪóŠ├õJ┼┼╬üżŌæųĖé(j©¼ng)żĘĪ󿥿ķż╦ź╬źżź║ż╬▒Ųūxż“£pż▒żõż╣ż»ż╩żļĪŻ╬╔żżż│ż╚żŽ▐kż─żŌż╩żżĪŻHBM3ż╚SoCż╚ż╬┤ųż╬š{(di©żo)▀`żŽJEDECæä│╩żŪ5.5mmµć┼┘ż╩ż╬żŪĪóHBMż╬źĘźĻź│ź¾ż¼Ė³ż▒żņżążĮż╬š{(di©żo)▀`ż¼żĄżķż╦äPżėżļż│ż╚ż╦ż╩żļĪŻźżź¾ź┐Ī╝ź▌Ī╝źČż╚żĘżŲĪóźĘźĻź│ź¾żĶżĻżŌŪ÷ż»║Ņ×æżŪżŁżļŃ~ĄĪź▌źĻź▐Ī╝ż“╗╚ż©żąĪóŪ█└■š{(di©żo)▀`ż“ø](m©”i)Į╠żŪżŁżļĪŻżĮż│żŪĪóTSMCżŽŃ~ĄĪźżź¾ź┐Ī╝ź▌Ī╝źČż“├ōżżżŲŪ█└■┴žż╬ø](m©”i)Į╠ż“┐▐ż├ż┐ĪŻŃ~ĄĪź▌źĻź▐Ī╝ż“äh▓┴żĘż┐±T▓╠Īó28GHzż½żķ56GHzżžż╚╝■āS┐¶ż“æųż▓żļż╦“£żżĄō╝║żŽĪóż│żņż▐żŪż╬źĘźĻź│ź¾źżź¾ź┐Ī╝ź▌Ī╝źČż╚Ų▒══Įj(lu©░)żŁż»ż╩żļż¼ĪóĖĮėX(ju©”)ż╬Ū÷żżźĘźĻź│ź¾źżź¾ź┐Ī╝ź▌Ī╝źČżĶżĻżŽŠ«żĄżżĪŻ

└Ķ├╝źčź├ź▒Ī╝źĖżŪżŽĪóSoCźūźĒź╗ź├źĄż╦Įj(lu©░)═Ų╬╠3╝ĪĖĄźßźŌźĻż╬HBMĪ╩High BandwidthĪĪMemoryĪ╦ż¼╗╚ż’żņżŲż¬żĻĪóżĮżņżŌHBM3ż╚żżż”║ŪĮj(lu©░)źąź¾ź╔╔²ż¼819GB/╔├ż╚Č╦żßżŲ╣Łżż3╝ĪĖĄźßźŌźĻżŪżóżļĪŻż│ż╬ż┐żßŪ█└■ż¼źŪĪ╝ź┐Å]┼┘ż“═Ņż╚ż╣ż│ż╚żŽß׿Ążņż╩żżĪŻ

TSMCżŽźżź¾ź┐Ī╝ź▌Ī╝źČæųż╦ź┴ź├źūż“ĮĖ└čż╣żļż│ż╬Č\Įčż“CoWoSĪ╩Chip on Wafer on SubstrateĪ╦Č\Įčż╚Ō}ż¾żŪżżżļż¼ĪóSoCżõź┴ź├źūźņź├ź╚ż╚HBMż“ĮĖ└čż╣żļ├ō²ŗżŪżŽĮj(lu©░)╬╠ż╦╗╚ż’żņżĮż”ż└ĪŻCoWoSČ\Įčż╦ż¬ż▒żļŃ~ĄĪźżź¾ź┐Ī╝ź▌Ī╝źČżŽĪóźĘźĻź│ź¾ż╚źūźĻź¾ź╚övŽ®┤łż╚ż╬ÕX╦──źĘĖ┐¶ż╬░Ńżżż╦żĶżļ▒■╬üż“┤╦Ž┬ż╣żļźąź├źšźĪż╬╠“│õżŌĘeż─ż╚żĘżŲżżżļĪŻ

╝┬║▌Īóźżź¾ź┐Ī╝ź▌Ī╝źČż╬║ŲŪ█└■┴žż╦ż¬żżżŲ┐«ęÄ(gu©®)┴žż“┼┼Ė╗┴žĪ”└▄├Ž┴žżŪČ┤żÓż│ż╚ż╦żĶżĻĪó7.2Gbpsż╬┐«ęÄ(gu©®)ż╬źóźżź└źżźõź░źķźÓżŪż╬ź╬źżź║ż╚źĖź├ź┐Ī╝żŽČ╦żßżŲŠ»ż╩ż½ż├ż┐ĪŻżĄżķż╦╣Ōča(b©│)╩▌┤╔żõ╣Ōča(b©│)Ų░║ŅĪóča(b©│)┼┘źĄźżź»źļż╩ż╔ż╬╗Ņ┘xż“╣įż├ż┐±T▓╠Īó╔į╬╔ē俎╚»Ö┌żĘż╩ż½ż├ż┐ż╚żżż”ĪŻż▐ż┐Įj(lu©░)żŁż╩ź└źżźĄźżź║ż╬źšźĻź├źūź┴ź├źū╝┬äóżĘż┐SoCż╚╚µż┘żŲżŌĪóźĘźĻź│ź¾ż╚źūźĻź¾ź╚┤łż╚ż╬ÕX╦──źĘĖ┐¶ż╬║╣ż“Ń~ĄĪźżź¾ź┐Ī╝ź▌Ī╝źČż¼źąź├źšźĪż╚żĘżŲĄ█╝²żĘż┐ż│ż╚żŪ▒■╬üżŽŠ»ż╩ż½ż├ż┐ż╚żĘżŲżżżļĪŻż▐ż┐ĪóźĘź▀źÕźņĪ╝źĘźńź¾ż└ż¼Īó4ź┴ź├źūż╬SoCż╚20ź┴ź├źūż╬HBM3Eż“Īó88.5mmĪ▀78.5mmĪ╩źņź┴ź»źļ8ĮŚ╩¼Ī╦ż╚żżż”ĄĮj(lu©░)ż╩Ń~ĄĪźżź¾ź┐Ī╝ź▌Ī╝źČæųż╦źčź├ź▒Ī╝źĖżĘż┐Šņ╣ńżŪżŌ╚┐żĻżŽ║ŪĮj(lu©░)59µmż╚Š»ż╩żżż╚żĘżŲżżżļĪŻ

║Żövż╬╚»╔ĮżŽĪó2022ŃQIMSIĪ╩┼┼╗ę╝┬äó╣®│žĖ”ē|ĮĻĪ╦ź¬Ī╝źūź¾źšź®Ī╝źķźÓż╦ż¬ż▒żļØŖ╩╠╣ų▒ķż╚żĘżŲJengĢ■(hu©¼)ż¼ÅBżĄżņż┐żŌż╬ĪŻ╣ų▒ķ├µż╦ź╣źķźżź╔ż“ź│źįĪ╝żĘżŲ═▀żĘż»ż╩żżż╚Įęż┘żŲżżż┐ż┐żßĪó┐▐ż“┐ā(j©®)ż╣ż│ż╚ż¼żŪżŁż╩ż½ż├ż┐ż│ż╚żŽ╗─Ū░żŪżóżļż¼ĪóJengĢ■(hu©¼)żŽ╣ų▒ķż╬║ŪĖÕż╦Īóź¼źķź╣źżź¾ź┐Ī╝ź▌Ī╝źČż╬▓─ē”└Łż╦ż─żżżŲ╩╣ż½żņż┐ä®╠õż“Šę▓żĘżĶż”ĪŻŲ▒Ģ■(hu©¼)żŽĪųźżź¾źįĪ╝ź└ź¾ź╣ż¼─Ńżżż╚żżż”┼└żŪżŽź¼źķź╣żŽ═źżņżŲżżżļż¼Īó╠õ¼öżŽź»źķź├ź»ż╬╚»Ö┌żŪżóżĻĪóżĮżņż“╦╔ż░ż┐żßż╬┼Ļ½@ż¼Įj(lu©░)żŁżżĪŻżĮż╬┼Ļ½@ż“ż╔ż”öv╝²ż╣żļż½ż¼╠õ¼öżŪżóżĻĪó┐ĘźūźĒź╗ź╣żŽżŪżŁżļĖ┬żĻ╗╚żżż┐ż»ż╩żżĪūż╚Įęż┘żŲżżżļĪŻ

╗▓╣═½@╬┴

1. ĪųNvidiaĪó║Ū┐ĘGPUÄźCPUÄźź═ź├ź╚ź’Ī╝ź»ź┴ź├źūżŪ└ż─c║Ūäė(d©░ng)ż╬ź│ź¾źįźÕĪ╝ź┐ż“║ŅżļĪūĪóź╗ź▀ź│ź¾ź▌Ī╝ź┐źļ (2022/03/25)