TSMCż¼28nmźūźĒź╗ź╣ż“ź▓Ī╝ź╚źķź╣ź╚żŪ╣Į├█Īó20nm░╩▓╝ż╬Ė½─╠żĘżŌĖņżļ

TSMCż¼28nmźūźĒź╗ź╣ż╦ż¬żżżŲź▓Ī╝ź╚źķź╣ź╚ż“┬ō(li©ón)┘Iż╣żļż│ż╚ż“╚»╔ĮżĘż┐ĪŻ7ĘŅ2Ų³│½╠¢ż╣żļTSMC2010 Technology Symposium Japanż╦└Ķż└ż├żŲĪó1Ų³ż╦źßźŪźŻźóĖ■ż▒ż╦żĮż╬▄ć═ūż“╚»╔ĮżĘż┐ż¼ĪóźßźŪźŻźóż╦×┤żĘżŲź©ź¾źąĪ╝ź┤ż“ż½ż▒Īó╦▄Ų³┘ćĖßż“Ęeż├żŲ╚»╔Įż╚ż╩ż├ż┐ĪŻ

TSMCż╬CTOżŪżóżļJack SunĖF╗╬

TSMCż¼║Żöv£½żķż½ż╦żĘż┐ż╬żŽ28nmCMOSźūźĒź╗ź╣ż“Īónź┴źŃź¾ź═źļź╚źķź¾źĖź╣ź┐ż╬ź▓Ī╝ź╚ż“n+Īópź┴źŃź¾ź═źļź╚źķź¾źĖź╣ź┐ż╬ź▓Ī╝ź╚ż“p+ż╬źßź┐źļź▓Ī╝ź╚żŪ╣Į└«ż╣żļź▓Ī╝ź╚źķź╣ź╚ż╬źūźĒź╗ź╣ż“║╬├ōż╣żļż│ż╚ĪŻź▓Ī╝ź╚źķź╣ź╚żŽźūźĒź╗ź╣ż¼╩Ż╗©ż╦ż╩żļżŁżķżżżŽżóżļżŌż╬ż╬ĪónĪóp╬Šź┴źŃź¾ź═źļż╬ź▓Ī╝ź╚źßź┐źļż╬╗┼Ą£┤ž┐¶ż“Ęeż┴żóż▓żķżņżļöĄ╝░ż“╗╚ż©żļż┐żßĪóź▓Ī╝ź╚źĻĪ╝ź»┼┼╬«ż╬æųĖéż“═▐ż©żķżņżļż╚żżż”źßźĻź├ź╚ż¼żóżļĪŻżŌż┴żĒż¾Īóź▓Ī╝ź╚└õ▒’╦ņż╦żŽhigh-k║Ó╬┴ż“├ōżżżļĪŻ

Ų▒╝ęR&D├┤┼÷CTOĘ¾VPż╬Jack SunĢ■ż╦żĶżļż╚ĪóĪųź▓Ī╝ź╚źšźĪĪ╝ź╣ź╚źūźĒź╗ź╣ż“╗╚ż├ż┐ż╚ż│żĒżŽż”ż▐ż»żżż├żŲżżż╩żżż╚╩╣ż»ĪŻż│ż”żżż├ż┐╬“╗╦ż½żķ│žżėĪó┼÷╝꿎ź▓Ī╝ź╚źķź╣ź╚źūźĒź╗ź╣ż“┬ō(li©ón)ż¾ż└Īūż╚Įęż┘ż┐ĪŻ

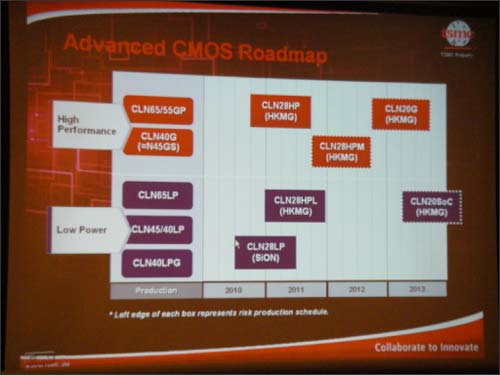

28nmż╬high-k/źßź┐źļź▓Ī╝ź╚Ī╩HKMGĪ╦źūźĒź╗ź╣ż╦żŽ3ż─ż╬ź¬źūźĘźńź¾ż¼żóżĻĪóżĮżņżŠżņ╣Ō└Łē”┴└żżż╬CLN28HPĪó╣Ō└Łē”źŌźąźżźļĖ■ż▒ż╬CLN28HPMĪó╣Ō└Łē”─ŃŠ├õJ┼┼╬üż╬CLN28HPLż¼żóżļĪŻCLN28HPźūźĒź╗ź╣żŽ2010ŃQŗī4╗═╚Š┤³ż╦╬╠ŠÅ│½╗Žż╣żļ╝Ŗ▓Ķż└ĪŻż┐ż└żĘĪó28nmźūźĒź╗ź╣ź¬źūźĘźńź¾żŽż│żņżķż¼ĮķżßżŲżŪżŽż╩żżĪŻ─ŃŠ├õJ┼┼╬ü┴└żżż╬CLN28LPż╚Ō}żążņżļź▓Ī╝ź╚└õ▒’╦ņż╦“£═Ķż╬SiONż“╗╚ż├ż┐źąĪ╝źĖźńź¾żŽ║ŪŖZĪó╬╠ŠÅż“│½╗ŽżĘż┐ĪŻ

TSMCż╬28nmĪĪCMOSźĒĪ╝ź╔ź▐ź├źū

28nmźūźĒź╗ź╣żŪ─_═ūż╦ż╩żļż│ż╚żŽĪóźŪźČźżź¾źļĪ╝źļż╬öU╠¾Ī╩RDRĪ╦ż“└▀ż▒żļż│ż╚żŪźūźĒź╗ź╣źąźķż─żŁż“żżż½ż╦žōżķż╣ż½ż╚żżż”ż│ż╚ż╦┐įżŁżļż╚żżż”ĪŻż│żņż▐żŪRDRż“└▀ż▒żŲźŪźČźżź¾ż“öU╠¾ż╣żļż╚ź╚źķź¾źĖź╣ź┐ż“ĮĖ└č▓ĮżĘż╦ż»ż»ż╩żļż╚żżż’żņżŲżżż┐ż¼Īó28nmżŪżŽĄšż╦źūźĒź╗ź╣źąźķż─żŁż¼ĮjżŁż»ż╩ż├żŲżĘż▐ż”ĪŻRDRż“└▀ż▒ż╩ż▒żņżąĪóŠ├õJ┼┼╬üĪóŲ░║ŅÅ]┼┘ĪóźĻĪ╝ź»┼┼╬«Īó╩Ōé╬ż▐żĻż╩ż╔ż¼ĄKż»ż╩żļż┐żßż└ż╚SunĢ■żŽĖ└ż”ĪŻRDRż╚żĘżŲżŽ╝Īż╬4╣Óų`ż╦öUĖ┬ż“└▀ż▒żļĪ©

1.ź▌źĻźĘźĻź│ź¾ż╬Ė■żŁż“▐köĄĖ■ż╦┬Ęż©żļż│ż╚

2.Ų▒▐k│╚ÜgĀC└čæųż╬ź╚źķź¾źĖź╣ź┐ż╬ź┴źŃź¾ź═źļ─╣ż“Ų▒▐kż╦ż╣żļż│ż╚

3.ź▌źĻźĘźĻź│ź¾ż╬┤ų│ųż“▐k─Ļż╦ż╣żļż│ż╚

4.│╚Ügōļ░Ķż“»éż▐ż├ż┐Ę┴ż╦┼²▐kż╣żļż│ż╚

źŪźČźżź¾źļĪ╝źļź┴ź¦ź├ź»żŽ20nm╗■┬Õż╦żŽĮjŠ}EDAź┘ź¾ź└Ī╝ż┐ż┴ż╚ż╬ź│źķź▄źņĪ╝źĘźńź¾żŽ’Lż½ż╗ż╩żżż╚żĘżŲżżżļĪŻż┐ż└żĘĪóż╔ż╬EDAź┘ź¾ź└Ī╝ż╚┴╚żÓż╬ż½ź╗ź▀ź│ź¾ź▌Ī╝ź┐źļżŽä®╠õżĘż┐ż¼ĪóSunĢ■żŽ┼·ż©ż“ķcż▒ż┐ĪŻ

28nmż╬╝Īż╬źūźĒź╗ź╣│½╚»ż╦żŌĖ└Ą┌Īó22nmżŽź╣źŁź├źūżĘżŲ20nmżž╚¶żųż╚SunĢ■żŽĮęż┘ż┐ĪŻĪųż│żņżŽź┴ź├źūź│ź╣ź╚ż╬Ė·╬©ż¼╬╔żżż½żķżŪĪóŲ▒żĖź”ź¦Ī╝źŽźĄźżź║żŪ╚µ│ėż╣żļż╚22nmżĶżĻżŌ20nmż╦ż╣żļż╚ź┴ź├źūż╬╠®┼┘żŽ20%żŌ╗\▓├ż╣żļż│ż╚ż¼ż’ż½ż├ż┐Īūż╚żĘżŲżżżļĪŻ

20nmż▐żŪżŽķ]┐╗ArFźĻźĮź░źķźšźŻż“╗╚ż©żļż└żĒż”ż¼Īó20nmż¼żŌżŽżõāS─╣Ė┬─cż└żĒż”ż╚żĘżŲĪóżĮżņ░╩æTż╬źĻźĮź░źķźšźŻż╦ż─żżżŲżŽEUVż╚MEBĪ╩ź▐źļź┴źėĪ╝źÓż╬┼┼╗ęźėĪ╝źÓŽ¬Ė„─ŠķWĪ╦ż╬2╦▄╬®żŲżŪ╣įż»ĪŻEUVżŽź¬źķź¾ź└ASMLż╬NXE3100ż“2011ŃQż╬┴ßżż╗■┤³ż½żķ╗╚żż╗ŽżßĪó20nmĪó14nmźūźĒź╗ź╣żŪżŽEUVż╬źūźĻźūźĒź└ź»źĘźńź¾├ōż╦2012ŃQż½żķ╗╚żż╗Žżßżļ═Į─Ļż└ĪŻMEBż╦ż─żżżŲżŽĪó2009ŃQ7ĘŅż╦MAPPERźūźņźóźļźšźĪĄĪż╚żĘżŲ5keVĪó110źėĪ╝źÓż╬ź─Ī╝źļż“╗╚ż├żŲ╗ŅżĘżŲżżżļż¼ĪóźėĪ╝źÓż╬Čč▐k└ŁżŽhp45nmż╚hp30nmżŪ10%░╩ŲŌż└ż├ż┐ż╚żĘżŲżżżļĪŻżĄżķż╦ź▐źļź┴źėĪ╝źÓż“źóź├źūź░źņĪ╝ź╔ż╣żļż│ż╚ż╦żĶż├żŲĪó13,000źėĪ╝źÓżŪ10ĮŚ/╗■ż╬ź╣źļĪ╝źūź├ź╚ż“20nmĪó14nmź╬Ī╝ź╔żŪżŽżĄżķż╦æųż▓Ī󟻟ķź╣ź┐Ī╝▓Įż╣żļż│ż╚żŪ100ĮŚ/╗■ż╬ź╣źļĪ╝źūź├ź╚ż“ų`║Yż╚żĘżŲżżżļĪŻ

20nm░╩▓╝ż╦ż╩żļż╚ź│źķź▄żŽź▐ź╣ź╚ż╦ż╩żļĪŻ20nm╩šżĻż½żķź”ź¦Ī╝źŽź│ź╣ź╚żŽŠå╗\ż╣żļż½żķżŪżóżļĪŻźĻźĮź░źķźšźŻäóÅø│½╚»żŽĖ└ż”ż▐żŪżŌż╩ż»Īó3D ICżŪżŽĮjŠ}źóź╗ź¾źųźĻźŽź”ź╣ż╚ż╬ź│źķź▄ż╦żĶżĻäė╬üż╩źĄźūźķźżź┴ź¦Ī╝ź¾ż“║ŅżĻĪóźżź¾ź┐Ī╝ź▌Ī╝źČż╬Ń~╠ĄżŌ┤▐żßżŲĖĪŲżżĘżŲżżż»ĪŻż┐ż└żĘĪóż│ż│żŪżŌźóź╗ź¾źųźĻźŽź”ź╣ż╬ć@ØiżŽķcż▒ż┐ĪŻ║ŪĮķż╬├╩│¼żŪżŽźżź¾ź┐Ī╝ź▌Ī╝źČżŽØŁ═ūż└ż¼Īó╝Īż╬├╩│¼żŪżŽ─Š└▄źĒźĖź├ź»ż╚źßźŌźĻĪ╝ż╩ż╔ż“TSVżŪ└▄¶öż╣żļż╚ż▀żŲżżżļĪŻ

żĄżķż╦Ų³╦▄ż╬źßĪ╝ź½Ī╝ż╚żŽäóÅøĪ”║Ó╬┴źßĪ╝ź½Ī╝ż╚ż╬ź│źķź▄ż“╦Šż▀ĪóäóÅøĪó║Ó╬┴Īóź▐ź╣ź»ĪóźŪźąźżź╣?ji©”)±═²ż“┤▐żßČ©╬üżĘż┐żżż╚żĘżŲżżżļĪ?50mmź”ź¦Ī╝źŽż╦┤žżĘżŲżŌ║ŻżŽISMI SEMATECHż╚Č©╬üżĘżŲżżżļż¼Īó╣ŁżżźĄźūźķźżź┴ź¦Ī╝ź¾ż╚ż╬ź│źķź▄ż¼ØŁ═ūż╚ż▀żŲżżżļĪŻ