¾HĄĪē”▓ĮĪó╩Ż╣ń▓Į┐╩żÓ▒R─Ļ▀_

▒R─Ļ▀_ż╬└ż─cżŪżŌ╚ŠŲ│öüICż╚Ų▒══Īó¾HĄĪē”▓Įż¼┐╩ż¾żŪżżżļĪŻź¬źĘźĒź╣ź│Ī╝źūż╚ź╣ź┌ź»ź╚źķźÓźóź╩źķźżźČż“┼ļ║▄żĘż┐▒R─Ļ▀_żŽż│żņż▐żŪżŌżóżļż¼ĪóTektronixżŽż│żņżķż╦▓├ż©źĒźĖź├ź»źóź╩źķźżźČż╚Ūż┴TāSĘ┴ż╬źšźĪź¾ź»źĘźńź¾źĖź¦ź═źņĪ╝ź┐ĪóźūźĒź╚ź│źļźóź╩źķźżźČĪóDVMĪ╩źŪźĖź┐źļ┼┼░Ą╝ŖĪ╦ż╬ĄĪē”ż“┼ļ║▄żĘż┐▒R─Ļ▀_MDO3000źĘźĻĪ╝ź║ż“╚»ŪõżĘż┐ĪŻAgilent TechnologiesżŽźĖź├ź┐Ī╝░§▓├ĪóźŪźŻź©ź¾źšźĪźĘź╣ĪóĀq│▓┐«ęÄĖ╗Ī󟻟Ēź├ź»īÄŪ▄▀_ĪóCDRĪóźżź│źķźżźČż╩ż╔ż“┼ļ║▄żĘż┐źėź├ź╚ĖĒżĻ╬©▒R─Ļ▀_M8000źĘźĻĪ╝ź║ż“╚»ŪõżĘż┐ĪŻ

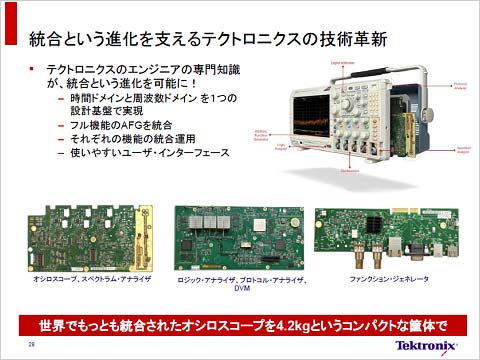

┐▐1ĪĪ1±śż╦Ž╗ż─ż╬ĄĪē”ż“┼ļ║▄ż╣żļTektronixż╬▒R─Ļ▀_

TektronixżŽĪóŽ╗ż─ż╬ĄĪē”ż“┼ļ║▄żĘż┐ż│ż╬▒R─Ļ▀_(┐▐1)ż“Īóź▀ź├ź»ź╣ź╔Ī”ź╔źßźżź¾Ī”ź¬źĘźĒź╣ź│Ī╝źūż╚Ō}żųĪŻ│½╚»żĘż┐═²ĮyżŽŲ¾ż─ż╬╠õ¼öż“▓“»éż╣żļż┐żßĪŻ▐kż─żŽĪóĖ▄Ąęż¼┼┼╗ęövŽ®ż╬Įą═ĶÉ║╣ńż“ź┴ź¦ź├ź»ż╣żļż╬ż╦ź¬źĘźĒżõź╣ź┌źóź╩ż└ż▒żŪżŽż╩ż»Ī󿥿▐żČż▐ż╩▒R─Ļ▀_ż“╗╚ż¬ż”ż╚ż╣żļż╚╝┬┘x╝╝ż¼▒R─Ļ▀_żŪżżż├żčżżż╦ż╩ż├żŲżĘż▐ż”ż│ż╚ĪŻżŌż”▐kż─żŽĪó▒R─Ļ▀_ż┤ż╚ż╦╗╚ż”öĄż¼░Ńż”ż┐żßźµĪ╝źČĪ╝żŽżĮżņżŠżņż“Ø{įużĘż╩ż▒żņżąż╩żķż╩żżż│ż╚ż└ĪŻŲ▒╝꿎Īóż│ż╬┐ĘĘ┐ź¬źĘźĒż“└ż─c║YØŹż╬▒R─Ļ▀_ż╦żĘż┐żżż╚żŌż»żĒżÓĪŻ

ż│ż╬MDO3000żŽĪó¾HĄĪē”ż“ź¬Ī╝źļźżź¾ź’ź¾żŪ┼ļ║▄żĘżŲżżżļż½żķż╚Ė└ż├żŲĪóź╣ź┌ź├ź»ż¼╬¶żļŚlżŪżŽż╩żżĪŻ╝■āS┐¶┬ė░ĶżŽ100MHzĪ┴1GHzĪó║Ū╣ŌźĄź¾źūźĻź¾ź░źņĪ╝ź╚żŽ5GźĄź¾źūźļ/╔├ĪóāSĘ┴ż“ŲDżĻ╣■ż¾żŪśŗ┐Ęż╣żļÅ]┼┘żŽ28╦³āSĘ┴/╔├ż╚Å]żżĪŻż▐ż┐Īó╚»Ö┌╔č┼┘ż╬¾HżżāSĘ┴ż“śĘĪ󊻿╩żżāSĘ┴ż“×EżŪ╔ĮĖĮż╣żļż¼ĪóźĄĪ╝źĖżõāį┼Ž┼¬ż╩źčźļź╣ż╩ż╔ż╬╔č┼┘ż╬Č╦żßżŲŠ»ż╩żżāSĘ┴ż╦×┤żĘżŲżŌ▓½┐¦żŪų`╬®ż┐ż╗żļżĶż”ż╩┐¦╗╚żżż“żĘżŲżżżļĪŻ╔ķ▓┘═Ų╬╠ż¼3.9pFżĘż½ż╩żżźūźĒĪ╝źųż“╗╚ż”ż│ż╚żŪĪóź¬Ī╝źąĪ╝źĘźÕĪ╝ź╚żõźóź¾ź└Ī╝źĘźÕĪ╝ź╚ż╬Š»ż╩żżāSĘ┴ż“ćĶ╗ĪżŪżŁżļĪŻ

ż▐ż┐Īóź╣ź┌źóź╩ĄĪē”żŪżŽĪó╝■āS┐¶┬ė░Ķż“║YØŹżŪ9kHzĪ┴100MHzżóżļżżżŽ9kHzĪ┴200MHzĪó9kHzĪ┴350MHzĪó9kHzĪ┴500MHzĪó9kHz~1GHzż╬5¹|╬Ó├ō┴TżĘżŲżżżļĪŻżĄżķż╦ź¬źūźĘźńź¾żŪ╝■āS┐¶┬ė░Ķż“3GHzż▐żŪ╣Łż▓żļż│ż╚ż¼żŪżŁżļż╚żżż”ĪŻ╗■┤ųż╚Č”ż╦ź╣ź┌ź»ź╚źķźÓż╬╩č▓Įż“▓─£å▓Įż╣żļż│ż╚żŌżŪżŁżļĪŻ┬ė░Ķż“╣Łż▓żļż│ż╚żŪĪó▐k┼┘ż╦ź╣ź┌ź»ź╚źķźÓż“äC░·ż╣żļż┐żßāSĘ┴ż“┤░µ£ż╦▌ö’BżŪżŁżļĪŻ“£═Ķż╬10MHz┬ė░Ķż└ż╚▓┐övż½ż╦╩¼ż▒żŲŲDżĻ╣■żÓż┐żßĪó╗■┤ų┼¬ż╦ŲDżĻż│ż▄ż╣▓─ē”└Łż¼żóż├ż┐ĪŻ║Żövż╬ź¬źūźĘźńź¾ż╩żķ2.4GHzż╬Wi-FiżõBluetoothż╩ż╔ż╬āSĘ┴ż╬══╗ężŌż’ż½żļĪŻ

źĒźĖźóź╩żŪżŽĪó16ź┴źŃź¾ź═źļż╬źĒźĖź├ź»āSĘ┴ż“500MźĄź¾źūźļ/╔├ż╬źņĪ╝ź╚żŪćĶ╗ĪżŪżŁĪóźóź╩źĒź░ź┴źŃź¾ź═źļż╚ż╬╗■┤ų┴Ļ┤žżŌŲDżņżļĪŻż▐ż┐ĪóźĘźĻźóźļźąź╣ż╬ź╚źĻź¼żõźŪź│Ī╝ź╔ĪóźĄĪ╝ź┴ż╦żĶżĻر═²┴žż╬źčź▒ź├ź╚źŪĪ╝ź┐ż╚żĘżŲżŌĪóż▐ż┐źżź┘ź¾ź╚źŲĪ╝źųźļż╚żĘżŲżŌĖ½żļż│ż╚ż¼żŪżŁżļĪŻ║YØŹ┼¬ż╩I2CżõSPIĪóRS-232/422/485/UARTĪóCANĪóLINĪóFlexRayĪóUSB2.0ż╩ż╔ż╬æä│╩ż╦żŌ×┤▒■żĘżŲżżżļĪŻ

RFŲ■╬üżŽ1ź┴źŃź¾ź═źļż└ż¼Īóźóź╩źĒź░Ų■╬üżŽ║ŪĮj4ź┴źŃź¾ź═źļż▐żŪ├ō┴TżĘżŲżżżļĪŻż│ż╬×æēäźĘźĻĪ╝ź║żŪżŽĪ󟬟ʟĒż╚ź╣ź┌źóź╩żŽ║YØŹäó×óż└ż¼ĪóźĒźĖźóź╩żõŪż┴TāSĘ┴źšźĪź¾ź»źĘźńź¾źĖź¦ź═źņĪ╝ź┐żŽź¬źūźĘźńź¾żŪĪóżĮżņżŠżņż╬ź▄Ī╝ź╔ż“ŲDżĻ¤²ż▒żŲżŌżķż”Ī╩┐▐2Ī╦ĪŻDVMż╚╝■āS┐¶ź½ź”ź¾ź┐żŽź”ź¦źų┼ąŹ{ż╣żļż╚╠Ą╬┴żŪ╝{▓├żŪżŁżļĪŻ║ŪżŌźĒĪ╝ź©ź¾ź╔ż╬×æē俎╝■āS┐¶┬ė░Ķż¼║ŪĮj100MHzżŪżóżĻĪóżĮż╬▓┴│╩żŽ39╦³6000▀ģĪŻ

┐▐2ĪĪTektronixż¼─¾ČĪż╣żļĘQź▄Ī╝ź╔

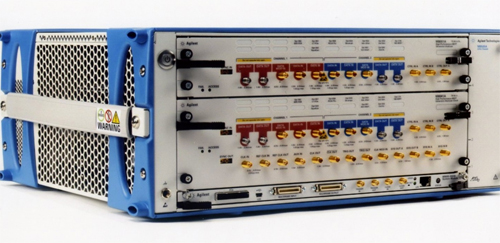

AgilentżŽ╣Ō╝■āSż╦äėżż×æēäż“Ęeż─┤ļČ╚żŪżóżļż¼Īóż│ż╬ż█ż╔╚»ŪõżĘż┐┴Ē╣ń┼¬ż╩źėź├ź╚ĖĒżĻ╬©▒R─Ļ▀_Ī╩BERTĪ¦bit error rateĪ╦(┐▐3)żŽĪó╣ŌÅ]źĘźĻźóźļźżź¾ź┐Ī╝źšź¦Ī╝ź╣ż╬ź┴ź¦ź├ź»ż╦╗╚ż”ĪŻź╣ź▐Ī╝ź╚źšź®ź¾żõź┐źųźņź├ź╚ż╩ż╔ż╬źŌźąźżźļ├╝¼ŹżŪżŽMIPIźżź¾ź┐Ī╝źšź¦Ī╝ź╣ĪóźŲźņźėż╩ż╔ż╬░cÖ┌ĄĪ▀_żŪżŽHDMIżõDisplayPortż╩ż╔ż╬źżź¾ź┐Ī╝źšź¦Ī╝ź╣Īóź│ź¾źįźÕĪ╝ź┐ĄĪ▀_żŪżŽPCI ExpressżõUSB3.1ĪóSATAż╩ż╔ż╬źżź¾ź┐Ī╝źšź¦Ī╝ź╣ĪóźŪĪ╝ź┐ź╗ź¾ź┐Ī╝żõź»źķź”ź╔ĄĪ▀_żŪżŽĪóFibre ChannelżõEthernetż╩ż╔ż╬źżź¾ź┐Ī╝źšź¦Ī╝ź╣ż“╗╚ż”ż¼Īóżżż║żņż╬╩¼╠ŅżŪżŌ╣ŌÅ]▓Įżžż╚Ų░żżżŲżżżļĪŻźŌźąźżźļżŪżŌ3GbpsĪó6/12Gbpsż╩ż╔ĪóPCIeżŪżŽ5Gbpsż½żķ8/16GbpsżžĪóEthernetżŪżŽ10Gbpsż½żķ100Gbpsżžż╚Ė■ż½ż├żŲżżżļĪŻ

┐▐3ĪĪAgilentż╬M8000źĘźĻĪ╝ź║BERT

ż│ż”żżż├ż┐▌xŠņż╦×┤▒■ż╣żļż┐żßĪóź▐źļź┴źņĪ╝ź¾ż“║╬├ōżĘż┐żĻĪóźŪĪ╝ź┐źņĪ╝ź╚ż“æųż▓ż┐żĻż╣żļĪŻM8000źĘźĻĪ╝ź║żŪżŽ║ŪĮj32Gbpsż▐żŪ×┤▒■▓─ē”żŪĪó║ŪĮj4ź┴źŃź¾ź═źļż╬ź▐źļź┴źņĪ╝ź¾▓Įż╦żŌ×┤▒■ż╣żļĪŻ

┐▐4ĪĪ┐«ęÄż╦ź╬źżź║żõŽ─ż“═┐ż©żŲż╔ż│ż▐żŪ┬čż©żķżņżļż½ż“─┤ż┘żļźėź├ź╚ĖĒżĻ╬©▒R─Ļ▀_ĪĪĮąųZĪ¦Agilent Technologies

┐«ęÄż“┴„┐«ż╣żļŠņ╣ńĪóźčź┐Ī╝ź¾źĖź¦ź═źņĪ╝ź┐żŪźčźļź╣š`ż“┴„żĻĮążĘĪóŲ▒╝┤ź▒Ī╝źųźļż╩ż╔ż╬┼┴┴„Ž®ż“┼┴ż’żĻĪó╚’▒R─ĻرĪ╩DUT: device under testĪ╦ż╬£p┐«övŽ®ż╦ŲŽż»ĪŻżĮż╬┐«ęÄżŽ┴„┐«övŽ®ż“ĘążŲĪóBERTżž╠ßżĄżņżļĪŻż│ż│żŪź©źķĪ╝ż“ĖĪĮążĘĪóżĮż╬ź©źķĪ╝╬©ż“▒R─Ļż╣żļĪŻźčźļź╣š`ż“┴„żĻĮąż╣źčź┐Ī╝ź¾źĖź¦ź═źņĪ╝ź┐żŪżŽĪ󿒿ȿ╚āSĘ┴ż“żęż║ż▐ż╗żļż┐żßż╬źŪźŻź©ź¾źšźĪźĘź╣övŽ®Īó░╠┴Ļź╬źżź║ż╬ĖĄż╦ż╩żļźĖź├ź┐Ī╝ż╩ż╔ż“─_øQż╣żļĪŻ

M8000źĘźĻĪ╝ź║ż╬BERTżŽĪó▒R─ĻżĘż┐żżDUTż¼ż╔ż│ż▐żŪŽ─ż¾ż└āSĘ┴ż╦×┤▒■żŪżŁżļż½ĪóżóżļżżżŽź▐źļź┴źņĪ╝ź¾ż╦ż¬ż▒żļź»źĒź╣ź╚Ī╝ź»żõź»źĒź├ź»ź╣źŁźÕĪ╝ż╩ż╔ż“äh▓┴ż╣żļĪŻBERTż╬├µż╦żŽĪó8ź┐ź├źūż▐żŪż╬źŪźŻź©ź¾źšźĪźĘź╣ĄĪē”ĪóźĖź├ź┐Ī╝ż╬ż─żżż┐ź»źĒź├ź»╚»Ö┌▀_Īóź╬źżź║żõź»źĒź╣ź╚Ī╝ź»ż“ź©ź▀źÕźņĪ╝źĘźńź¾ż╣żļĻJŠ─żŽ░§▓├ĄĪē”Ī╩Diff. mode interfaceż╚Com. Mode interfaceĪ╦ĪóCDRĪ╩Clock data recoveryĪ╦ż╩ż╔ż╬övŽ®ż“ŲŌē┼żĘżŲżżżļż┐żßĪó╩╠ż╬▒R─Ļ▀_ż“┬Ęż©żļØŁ═ūżŽż╩żżĪŻ

BERTż╬┐«ęÄż“£pż▒żļŖõżŪżŽĪóCTLEĪ╩continues time linear equalizerĪ╦ż╦żĶżļźóźżźčź┐Ī╝ź¾ż╬▌ö┘ćż“╣įżżĪóCDRżŪź»źĒź├ź»ż╚źŪĪ╝ź┐ż“╩¼▀`żĘĪóBERż“ź½ź”ź¾ź╚ż╣żļĪŻ