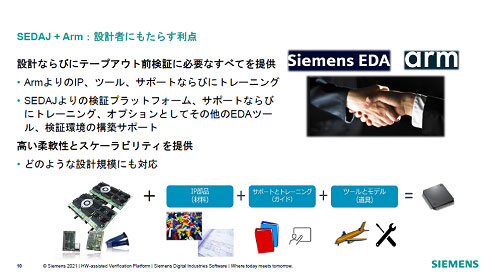

Armż╬IPź│źóż╚źĘĪ╝źßź¾ź╣EDAż╬ĖĪŠ┌źūźķź├ź╚źšź®Ī╝źÓż“Č”Ų▒żŪ─¾ČĪ

źĘĪ╝źßź¾ź╣ EDAźĖźŃźčź¾ż╚Armż╬Ų³╦▄╦Ī┐═żŪżóżļźóĪ╝źÓżŽĪóSoC│½╚»ż╚ĖĪŠ┌ż╬┤─ČŁż“Č”Ų▒żŪ─¾ČĪż╣żļż╚╚»╔ĮżĘż┐Ī╩┐▐1Ī╦ĪŻArmż╬─¾ČĪż╣żļCPUżõGPUż╩ż╔ż╬IPź│źóż“╗╚ż├żŲĪóSoCż“└▀╝ŖżĘżŲż▀ż┐żżź©ź¾źĖź╦źóż╦ż╚ż├żŲŖW▓┴ż╦Š}Ę┌ż╦└▀╝ŖżĘżõż╣ż»ż╩żļĪŻż▐ż║żŽIoT├ōż╬SoCż“│½╚»ż╣żļż┐żßż╬FPGAĖĪŠ┌ź▄Ī╝ź╔ż“─¾ČĪż╣żļĪŻ

┐▐1ĪĪźĘĪ╝źßź¾ź╣EDAż╚źóĪ╝źÓż¼SoCż╬éb═²└▀╝ŖĪ”ĖĪŠ┌żŪŠ}ż“┴╚żÓĪĪĮąųZĪ¦źĘĪ╝źßź¾ź╣EDAźĖźŃźčź¾ĪóźóĪ╝źÓ

ż│żņż▐żŪĪóLSI└▀╝ŖŪvż¼Armż╬IPź│źóż“╗╚ż├żŲĪóż╣ż░ż╦SoCż“╗Žżßżļż│ż╚ż¼ż╩ż½ż╩ż½żŪżŁż╩ż½ż├ż┐ĪŻArmż½żķźķźżź╗ź¾ź╣─¾ČĪżĘżŲżŌżķż├żŲżŌĪó┤³┬įżĘżŲżżż┐└Łē”żõĄĪē”ĪóŠ├õJ┼┼╬üż╩ż╔ż“╝┬ĖĮżŪżŁż║Īóż│ż¾ż╩żŽż║żŪżŽż╩ż½ż├ż┐Īóż╚żżż”╔į╦■ż“Ęeż├ż┐└▀╝ŖŪvż¼żżżŲżŌ×┤▒■żŪżŁż╩ż½ż├ż┐ĪŻż│ż╬ż┐żßĪó┘ć╝░ż╩źķźżź╗ź¾ź╣ż“±TżųØiż╦Īóż┴żńż├ż╚╗╚ż├żŲż▀żĶż”Īóż╚żżż”╗┼²Xż▒ż¼AFAĪ╩Arm Flexible AccessĪ╦żŪżóżļĪŻ╝┬║▌ż╦éb═²└▀╝Ŗż“╣įżżĪóSoC├ōż╬RTLż“įuż┐ż╚żĘżŲżŌĪóéb═²ż¼┘ćżĘż»źūźĒź░źķź▀ź¾ź░żĘżŲżĄżņżŲżżżļż╬ż½ĖĪŠ┌żĘżŲż▀żļØŁ═ūż¼żóżļĪŻż│ż╬ż┐żßĪóźóĪ╝źÓżŽźĘĪ╝źßź¾ź╣ż╚┴ĻÕiżĘżŲżŁż┐ĪŻ

Ąņźßź¾ź┐Ī╝ź░źķźšźŻź├ź»ź╣źĖźŃźčź¾żŪżóżļźĘĪ╝źßź¾ź╣EDAźĖźŃźčź¾żŽĪóźŽĪ╝ź╔ź”ź©źóż“ĖĪŠ┌ż╣żļź©ź▀źÕźņĪ╝ź┐Veloceż╦Īó│½╚»ĖĪŠ┌ź▄Ī╝ź╔żõźĮźšź╚ź”ź©źóĖĪŠ┌ź─Ī╝źļż╩ż╔żŌ╝{▓├żĘżŲżŁż┐ĪŻżĘż½żĘĪóźĘĪ╝źßź¾ź╣EDAżŽIPż“Ęeż├żŲżżż╩żżż┐żßĪóż╣ż░ż╦└▀╝ŖżŪżŁżļ┤─ČŁżŪżŽż╩ż½ż├ż┐ĪŻ

║ŻövĪóarmż╬IPźĄĪ╝źėź╣AFAż╚ĪóźĘĪ╝źßź¾ź╣ż╬Veloce proFPGAĖĪŠ┌źūźķź├ź╚źšź®Ī╝źÓż“╗╚ż├żŲSoCż“└▀╝ŖĖĪŠ┌ż╣żļ┤─ČŁż“─¾ČĪż╣żļĪŻźóĪ╝źÓż¼źĘĪ╝źßź¾ź╣ż╦─¾░Ųż“Ęeż┴ż½ż▒ż┐ż╬żŽĪóarmż╬Ęeż─IPź│źóż¼┬Šż╬EDAźķźżźąźļ2╝ęż╚żŽ░ŃżżĪóźĘĪ╝źßź¾ź╣ż╬IPżŽarmż╬IPź│źóż╚żŽĒö╣ńżĘż╩żżż┐żßż└ż╚żżż”ĪŻż▐ż┐ĪóarmśO┐╚ż╬śOØiż╬│½╚»ź▄Ī╝ź╔żŽĘeż├żŲżżżļż¼Īó╠▀żŽ╠▀▓░żŪźĘĪ╝źßź¾ź╣ż╬öĄż¼ĖĪŠ┌Č\Į迎żĘż├ż½żĻżĘżŲżżżļż┐żßĪó║Żövż╬ź│źķź▄ż╚ż╩ż├ż┐ĪŻ

AFAżŽĪóŃQ▓±õJż“ܦ╩¦ż”ż└ż▒żŪĪóSoC│½╚»ż╬ź─Ī╝źļżõźĄź▌Ī╝ź╚Ī”ź╚źņĪ╝ź╦ź¾ź░źĄĪ╝źėź╣ż╩ż╔ż¼£pż▒żķżņżļż┐żßĪó╬╠ŠÅż╦Ų■żļ├╩│¼żŪĮķżßżŲ┘ć╝░ż╩źĒźżźõźĻźŲźŻõJ├ōż“Ė½└čżŌżļż│ż╚ż¼żŪżŁżļĪŻż▐ż┐╠õ¼öż¼ÅŚżŁż┐╗■żŽĪóArmż╚żŌ─Š└▄ÅBż“ż╣żļż│ż╚ż¼żŪżŁżļĪŻźóĪ╝źÓż¼─¾ČĪż╣żļCPU/GPUź│źóżõ╝■╩šIPĪóر═²IPżŽ┐▐2ż╦┐āż╣ż╚ż¬żĻżŪżóżļĪŻ

┐▐2ĪĪArmż¼─¾ČĪż╣żļIP×æēäĘ▓ĪĪĮąųZĪ¦źóĪ╝źÓ

źĘĪ╝źßź¾ź╣ż╬Veloce proFPGAźūźĒź╚ź┐źżźįź¾ź░│½╚»ź▄Ī╝ź╔żŽĪóRTLĮą╬üż▐żŪż╬éb═²└▀╝Ŗż“ĖĪŠ┌ż╣żļżŌż╬żŪĪóź═ź├ź╚źĻź╣ź╚żõéb═²╣ń└«żŽ░Ęż’ż╩żżĪŻArmż╚┴╚żÓż│ż╚żŪĪóArmż╬CPUź│źóżõGPUź│źóĪóżĮż╬┬Šż╬IPż╩ż╔ż“┼ļ║▄żĘĪóSoCż“┴╚żÓØiż╦éb═²└▀╝Ŗż¼┘ćżĘż»Į±ż½żņĪóéb═²Ų░║ŅżŪżŁżļż½ż╔ż”ż½ż“ĖĪŠ┌ż╣żļĪŻ

▐k╚╠ż╦ĪóSoCż“└▀╝ŖżĘżŲż▀żļŠņ╣ńż╦żŽĪóżżżŁż╩żĻźĘźĻź│ź¾ż╦╝┬äóż╣żļż╬żŪżŽż╩ż»Īó║ŪĮķż╦FPGAżŪéb═²ż“┴╚ż¾żŪĪóżĮż╬éb═²ż¼┘ćżĘżżż½ż╔ż”ż½ż“ĖĪŠ┌żĘżŲż¬ż»ØŁ═ūż¼żóżļĪŻ┘ćżĘż▒żņżąĪóź═ź├ź╚źĻź╣ź╚żóżļżżżŽéb═²╣ń└«ż╩ż╔żŪövŽ®┐▐ż╦═Ņż╚żĘĪó║ŪĮ¬┼¬ż╦Ū█ÅøŪ█└■Ī”źņźżźóź”ź╚ż“║čż▐ż╗ĪóOPCż╩ż╔ż╬▌ö┘ćż“▓├ż©żŲźšź®ź╚ź▐ź╣ź»źŪĪ╝ź┐ż╚żĘżŲĮą╬üż╣żļĪŻ

│½╚»ź▄Ī╝ź╔ż╦╗╚├ōż╣żļFPGAżĮż╬żŌż╬ż¼Xilinxż╬Zynq×æēäż╬żĶż”ż╦CPUŲŌē┼ż╬FPGAżŪżŌĪóĮŃ┐Ķż╬FPGAżŪż╔ż┴żķżŪżŌ×┤▒■▓─ē”ż└ż╚żĘżŲżżżļĪŻż▐ż┐ĪóXilinxż└ż▒żŪżŽż╩ż»ĪóIntelĪ╩ĄņAlteraĪ╦ż╬FPGAżŌ┼ļ║▄żŪżŁżļĪŻ

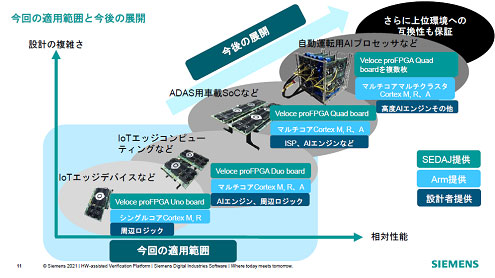

ż▐ż┐źĘĪ╝źßź¾ź╣ż╬─¾ČĪż╣żļVeloce proFPGAżŪżŽFPGAż¼1Ė─Īó2Ė─Īó4Ė─ż“┼ļ║▄żĘż┐ź▐źČĪ╝ź▄Ī╝ź╔ż“─¾ČĪż╣żļĪŻźµĪ╝źČĪ╝ż╬╦ŠżÓSoCż╬æä╠Žż╦żĶż├żŲ┬ō┘Iż╣żļĪŻ║ŪĮj4Ė─FPGAż“┼ļ║▄żĘż┐ź▄Ī╝ź╔ż“║ŪĮj5ĮŚż▐żŪ╝²═ŲżŪżŁżļźŌźĖźÕźķĪ╝öĄ╝░ż“ż╚ż├żŲż¬żĻĪó║ŪĮj8▓»ź▓Ī╝ź╚ż▐żŪż╬└▀╝Ŗæä╠Žż╬SoCż▐żŪ×┤▒■żŪżŁżļĪŻ

┐▐3ĪĪ║ŻĖÕżŽżĄżķż╦æä╠Žż╬ĮjżŁż╩SoCż╬└▀╝ŖĖĪŠ┌ż╦żŌ×┤▒■żĘżŲżżż»ĪĪĮąųZĪ¦źĘĪ╝źßź¾ź╣EDAźĖźŃźčź¾

║ŻövżŽIoTĖ■ż▒ż╬SoCż“┴└ż├ż┐żŌż╬ż└ż¼Īó║ŻĖÕĪ󿥿ķż╦æä╠Žż╬ĮjżŁżżADAS├ōż╬SoCżõśOŲ░▒┐┼ŠĖ■ż▒ż╬SoCż╩ż╔æä╠Žż╚└Łē”ż¼╣Ōżż×æēäż╬źĄź▌Ī╝ź╚żžż╚│╚ĮjżĘżŲżżż»Ī╩┐▐3Ī╦ĪŻ║Żövż╬─¾Ę╚żŽŲ³╦▄╦Ī┐═Ų▒╗╬ż╬ź│źķź▄ż└ż¼Īó╬Š╦▄╝ęż╚żŌ╬Š╝ęż╬ź│źķź▄ż“└ż─c·t│½ż╣żļŠņ╣ńż╬╗▓╣═ż╦żĘżĶż”ż╚║ŻĖÕż╬Ęą░▐ż“ÅRų`żĘżŲżżżļż╚żżż”ĪŻ