źßź¾ź┐Ī╝ź░źķźšźŻź├ź»ź╣Īó3D ICŲŌż╬ĘQź┴ź├źūż“źŲź╣ź╚żŪżŁżļź─Ī╝źļż“│½╚»

ä▌źßź¾ź┐Ī╝ź░źķźšźŻź├ź»ź╣╝꿎ĪóTSV└▄¶öż“ŠW├ōż╣żļ3╝ĪĖĄ(3D)ICż╦ż¬żżżŲźčź├ź▒Ī╝źĖź¾ź░ĖÕżŪżŌźčź├ź▒Ī╝źĖŲŌż╦żóżļĘQź┴ź├źūż“źŲź╣ź╚żŪżŁżļżĶż”ż╩Č\Įč└’ŠSż“Globalpress╝ń╠¢ż╬źūźņź╣ź╗ź▀ź╩Ī╝e-Summit2011ż╦ż¬żżżŲ£½żķż½ż╦żĘż┐ĪŻ

┐▐1ĪĪźßź¾ź┐Ī╝CEOż╬Walden RhinesĢ■ (║Ė) ż╚ź▐Ī╝ź▒źŲźŻź¾ź░źŪźŻźņź»ź┐ż╬Stephen PaterasĢ■ (īÜ)

3╝ĪĖĄICżŽĪó╚∙║┘▓ĮżŪź│ź╣ź╚ź└ź”ź¾ż“żĘż╦ż»ż»ż╩ż├żŲżŁż┐ż│ż╚ż╦×┤ż╣żļ▓“ż└ż╚żżż©żļĪŻźßź¾ź┐Ī╝ź░źķźšźŻź├ź»ź╣ż╬CEOżŪżóżļWalden RhinesĢ■(┐▐1)żŽĪóż│żņż▐żŪż╬╚∙║┘▓Į’łĖ■żŪżŽ90nmźūźĒź╗ź╣żŪżŽØi└ż┬Õż╦╚µż┘47%ż╬ź│ź╣ź╚ź└ź”ź¾ż╦ż╩ż├ż┐ż¼Īó65nmżŪ12%Īó45nmżŪżŽ9%Īó32nmżŪ2.5%Īóż╚ź│ź╣ź╚ź└ź”ź¾ż╬╔²ż¼Š»ż╩ż»ż╩ż├żŲżŁż┐ż╚╗ž╝~żĘż┐ĪŻ22nmż╦ż╩żļż╚Ąšż╦2%ż╬ź│ź╣ź╚źóź├źūż╦ż╩żļż╚żżż”ĪŻź│ź╣ź╚ź└ź”ź¾żŽźķĪ╝ź╦ź¾ź░ź½Ī╝źųĪ╩Ø{▌^Č╩└■Ī╦ż╦▐pż├żŲ╝┬ĖĮżĘżŲżŁż┐ż¼Īó22nmż╬└ĶżŽČ\Įčż“Ø{▌^żĘżŲżŌ╚∙║┘▓Įż╦żĶżļź│ź╣ź╚ź└ź”ź¾żŽžMżĘż»ż╩ż├żŲżŁż┐ż╚żżż”Ślż└ĪŻ3D ICż¼żĮż╬ź│ź╣ź╚ź└ź”ź¾ż╬▓“ż╚ż╩żĻż”żļĪŻ

3╝ĪĖĄICż╬║ŪĮjż╬╠õ¼öżŽź│ź╣ź╚ż└ż╚żżż’żņżļż¼Īóź│ź╣ź╚ż“»éżßżļ═ū░°ż╬ż╩ż½żŪżŌ╩Ōé╬ż▐żĻż“żżż½ż╦│╬╩▌ż╣żļż½Īóż¼żĄżķż╦żĮż╬ź½ź«ż“É█żļĪŻ╬╔ēäź┴ź├źūż“3╝ĪĖĄ▓├╣®żĘż┐ĖÕżŪżŌ╬╔ēä/╔į╬╔ēäż“źŲź╣ź╚ż╣żļŠņ╣ńż╦Īó├▒ż╦└▄¶öż¼ż”ż▐ż»żżż├żŲżżżļż½ż╔ż”ż½ż└ż▒żŪżŽż╩ż»Īó╬Ńż©żąźßźŌźĻż╩żķźŲź╣ź╚źčź┐Ī╝ź¾─╠żĻż╬┼·ż©ż“Įąż╗żļż½ż╔ż”ż½żŌźŲź╣ź╚żĘż╩ż▒żņżąż╩żķż╩żżĪŻ╩Ż┐¶ż╬ź┴ź├źūż╬źŲź╣ź╚╗■┤ųż“ø]Į╠żĘĪóżĘż½żŌµ£żŲż╬ź╚źķź¾źĖź╣ź┐ż“ź┴ź¦ź├ź»żŪżŁżļżĶż”ż╦ź½źąĪ╝╬©ż“æųż▓ż╩ż▒żņżąż╩żķż╩żżĪŻ

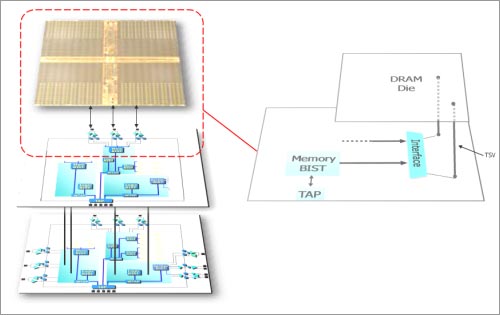

źĘź╣źŲźÓLSIż╬└▀╝ŖĪ”ĖĪŠ┌ź─Ī╝źļż“Š}²Xż▒żŲżŁż┐źßź¾ź┐Ī╝żŽĪó3D ICż“źŲź╣ź╚ż╣żļż┐żßż╬×æēäźĘźĻĪ╝ź║Tessentż“│½╚»żĘż┐ĪŻż│ż╬×æēäż“╗╚ż©żąĪóź╣ź┐ź├ź»żĄżņż┐╩Ż┐¶ż╬ź┴ź├źūż“│¼┴ž┼¬ż╦ź╣źŁźŃź¾żĘĪ󿥿ķż╦BISTĪ╩built-in self testĪ╦Š}╦ĪżŪżŌźŲź╣ź╚ż╣żļĪŻź┴ź├źūŲ▒╗╬ż“TSVżŪż─ż╩ż░3D ICż╦▓├ż©Īóźżź¾ź┐Ī╝ź▌Ī╝źČż“▓ż╣żļ2.5╝ĪĖĄż╬ICż╦żŌTessentżŽ╗╚ż©żļĪŻ

TessentżŪżŽż▐ż║ĪóźĒźĖź├ź»ź┴ź├źūż╬ź▓Ī╝ź╚övŽ®ż“żŪżŁżļż└ż▒µ£żŲź½źąĪ╝żĘĪóżĘż½żŌø]╗■┤ųżŪźŲź╣ź╚ż╣żļż│ż╚ż“źßź¾ź┐Ī╝żŽ╣═ż©ż┐ĪŻź½źąĪ╝╬©ż╬╣Ōżżī¦ō¶źķź¾ź└źÓźčź┐Ī╝ź¾ż“╚»Ö┌ż╣żļTessent LogicBISTż╚ĪóźŲź╣ź╚źŪĪ╝ź┐ż“żŪżŁżļż└ż▒ĮjżŁż»░ĄĮ╠żĘżŲźŲź╣ź╚╗■┤ųż“ø]Į╠żŪżŁżļź╣źŁźŃź¾źčź┐Ī╝ź¾ż“Ö┌└«ż╣żļTessent TestKompressż“┴╚ż▀╣ńż’ż╗ż┐ź─Ī╝źļż“├ō┴TżĘż┐ĪŻ

╝Īż╦ĪóźĒźĖź├ź»ż╚źßźŌźĻżõźóź╩źĒź░ICĪó╣ŌÅ]I/Oźżź¾ź┐Ī╝źšź¦Ī╝ź╣ICż╩ż╔ż“ź╣ź┐ź├ź»ż╣żļŠņ╣ńż╦×óż©żŲĪóźĒźĖź├ź»BISTż╚źßźŌźĻBISTĪóźóź╩źĒź░źŲź╣ź╚ż¬żĶżėźąź”ź¾ź└źĻź╣źŁźŃź¾źŲź╣ź╚ż“┴╚ż▀╣ńż’ż╗ż┐ĪŻż│żņżķż╬×æēäż╦żŽĪóTessent MemoryBISTż╚Tessent BoundaryScanĪóTessent PLLTestĪóTessent SerdesTestż╩ż╔ż¼żóżļĪŻż│żņżķż“╗╚ż”ż│ż╚ż╦żĶż├żŲĪóźŲź╣ź╚ź│ź▐ź¾ź╔ż“ĘQź┴ź├źūż╦┴„żĻĪóĘQź┴ź├źūż“─╠ż├żŲźŲź╣ź╚źčź┐Ī╝ź¾ż“┴„żĻ╣■żÓż│ż╚ż¼żŪżŁżļĪŻ║ŪĮjż╬źßźĻź├ź╚żŽĪó3D ICż“źčź├ź▒Ī╝źĖź¾ź░żĘż┐ĖÕżŪżĄż©Īóź┴ź├źūż┤ż╚ż╦źŲź╣ź╚żŪżŁżļż│ż╚żŪżóżļĪŻż│ż╬│¼┴ž┼¬ż╩Š}╦ĪżŽIEEE1149.1æä│╩ż╦ØŹżĖżŲżżżļĪŻ

┐▐2ĪĪźĒźĖź├ź»ż╦ĮĖ└čżĘż┐źßźŌźĻBISTż“╗╚żżDRAMż╦źŲź╣ź╚źčź┐Ī╝ź¾ż“┴„żĻ╣■żÓ

╬Ńż©żąĪóźĒźĖź├ź»ż╚ź╣ź┐ź├ź»żĘż┐źßźŌźĻż“źŲź╣ź╚ż╣żļŠņ╣ńż╦żŽĪóźĒźĖź├ź»ź┴ź├źūż╦ĮĖ└čżĘż┐źßźŌźĻBISTövŽ®ż“╗╚ż”(┐▐2)ĪŻż│ż╬Šņ╣ńĪó3D ICż╬I/O├╝╗ęż½żķźĒźĖź├ź»ź┴ź├źūż╬BISTövŽ®ż“Ų░ż½żĘĪóATPGĪ╩śOŲ░źŲź╣ź╚źčź┐Ī╝ź¾╚»Ö┌▀_Ī╦ż½żķźßźŌźĻ├ōż╬źŲź╣ź╚źčź┐Ī╝ź¾ż“┴„żĻ╣■żÓĪŻżĮż╬övŽ®ż½żķźßźŌźĻż╬źóź╔źņź╣źąź╣żõźŪĪ╝ź┐źąź╣ż“źóź╔źņź├źĘź¾ź░ż╣żļż│ż╚żŪĪóźßźŌźĻżžźŲź╣ź╚źčź┐Ī╝ź¾ż“┴„żĻ╣■żÓż│ż╚ż¼żŪżŁżļĪóż╚Ų▒╝ęźĘźĻź│ź¾źŲź╣ź╚źĮźĻźÕĪ╝źĘźńź¾ź║ŗ╠ńż╬×æēäź▐Ī╝ź▒źŲźŻź¾ź░źŪźŻźņź»ź┐żŪżóżļStephen PaterasĢ■(┐▐1īÜ)żŽĮęż┘żŲżżżļĪŻ