MicronĪó176┴žż╚żżż”║Ū╣Ō┴žż╬NANDźšźķź├źĘźÕż“źĄź¾źūźļĮą▓┘

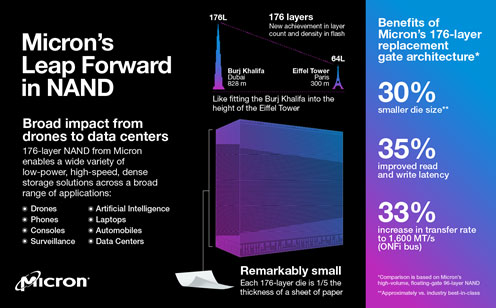

Micron Technologyż¼176┴žż╬NANDźšźķź├źĘźÕźßźŌźĻż╬Įą▓┘ż“│½╗ŽżĘż┐Ī╩╗▓╣═½@╬┴1Ī╦ĪŻż│żņż▐żŪżŌźŁź¬ź»źĘźóż╬112┴žżõ128┴žż╬│½╚»żŽżóż├ż┐ĪŻ×æēäżŪżŽ96┴žż╬NANDż¼Ų■Š}▓─ē”ż└ż¼Īó“£═Ķż╬║ŪĮj═Ų╬╠żĶżĻ40%░╩æųżŌĮjżŁż╩═Ų╬╠ż╬ź╣ź╚źņĪ╝źĖźŪźąźżź╣ż╚ż╩żļĪŻżĘż½żŌŲ╔ĮążĘĪ”Į±żŁ╣■ż▀ż╬ź╣źįĪ╝ź╔Ī╩źņźżźŲź¾źĘĪ╦żŽ35%░╩æųżŌÅ]żżż╚żżż”ĪŻźŪĪ╝ź┐ź╗ź¾ź┐Ė■ż▒SSDż“┴└ż”ĪŻ

┐▐1ĪĪ176┴žż“CMOSövŽ®æųż╦Ę┴└«żĘżŲżŌ╔ß─╠└Lż╬1/5ż╬Ė³żĄżĘż½ż╩żżĪĪĮąųZĪ¦Micron Technology

Micronż╬176┴žNANDźšźķź├źĘźÕżŽĪóż│żņż▐żŪż╬źóĪ╝źŁźŲź»ź┴źŃż╚żŽµ£ż»░█ż╩żĻĪóCMOSź╚źķź¾źĖź╣ź┐┴žż╬æųż╦Ę┴└«ż╣żļĪŻźŪĪ╝ź┐╬╠ż╬¾Hżż╔ķ▓┘żõ┤─ČŁżŪ░ę╬üż“╚»Ä¦ż╣żļĪŻ╬Ńż©żą╣Įļ]▓ĮźŪĪ╝ź┐ż╚ØÖ╣Įļ]▓ĮźŪĪ╝ź┐ż“▐kż─ż╦Č”┘Tż╣żļźŪĪ╝ź┐źņźżź»żõĪóźėź├ź░źŪĪ╝ź┐▓“└ŽĪóAIź©ź¾źĖź¾ż╬żĶż”ż╩▒■├ōżŪżóżļĪŻż▐ż┐Īó5GżŪżŽĪó¾H┐¶ż╬źóźūźĻ┤─ČŁżŪżŌ╬®ż┴æųż¼żĻżõź╣źżź├ź┴ź¾ź░ż¼╣ŌÅ]ż╦ż╩żļż┐żßĪó╗╚żż▒MŠ}Ī╩QoSĪ╦żŽż½ż╩żĻ╬╔ż»ż╩żļż╚żĘżŲżżżļĪŻ

║ŪĮj┼Š┴„źņĪ╝ź╚żŽĪó1,600 MT/sĪ╩źßź¼┼Š┴„/╔├Ī╦ż╚ONFIĪ╩Open NAND Flash InterfaceĪ╦źąź╣æųżŪŲ░║ŅżĘĪóMicronż╬“£═Ķż╬128┴žNAND×æēäżĶżĻżŌ33%╣ŌÅ]ż╦ż╩żļĪŻż│ż╬ż┐żßźĘź╣źŲźÓż╬ÅŚŲ░żõźóźūźĻź▒Ī╝źĘźńź¾źĮźšź╚ż╬└Łē”ż¼æųż¼żļĪŻśOŲ░┘ZźĘź╣źŲźÓż╦╗╚ż©żąĪóź©ź¾źĖź¾ż“ÅŚŲ░ż╣żļż╚Ų▒╗■ż╦║t║┬ż╦▒■┼·ż╣żļżĶż”ż╦ż╩żļĪŻ

MicronżŽż╣żŪż╦źĘź╣źŲźÓźßĪ╝ź½Ī╝ż╚Č”ż╦┐Ę×æēäż“┴╚ż▀╣■żÓ║ŅČ╚ż“╗ŽżßżŲż¬żĻĪóźšźĪĪ╝źÓź”ź©źóż“į~├▒ż╦źūźĒź░źķźÓżŪżŁżļżĶż”ż╦ż╣żļż┐żßĪó▐k╔«Į±żŁż╬żĶż”ż╩źĘź¾ź░źļźčź╣ż╬źūźĒź░źķźÓźóźļź┤źĻź║źÓż“│½╚»żĘż┐ĪŻż│żņż╦żĶżĻĪóźĘź╣źŲźÓźßĪ╝ź½Ī╝żŽźĮźĻźÕĪ╝źĘźńź¾ż╦┴ßż»┴╚ż▀╣■żÓż│ż╚ż¼żŪżŁĪó▌xŠņżžż╬Įą▓┘┤³┤ųĪ╩Time to marketĪ╦ż“ø]Į╠żŪżŁżļĪŻ

ź╗źļ╣Įļ]żŽź┴źŃĪ╝źĖź╚źķź├źūöĄ╝░ż└ż¼ĪóŲ╚śO│½╚»żĘż┐CMOSźóź¾ź└Ī╝źóźņźż╣Įļ]Ī╩CuA: CMOSövŽ®ŗ╩¼żĶżĻæųż╦źßźŌźĻź╗źļż“└▀ż▒ż┐╣Įļ]Ī╦ż“ż╚żļĪŻżĘż½żŌź’Ī╝ź╔└■ż╬┼┼Č╦ż“Īó“£═Ķż╬ź▌źĻźĘźĻź│ź¾ź▓Ī╝ź╚żŪżŽż╩ż»Īóźßź┐źļź▓Ī╝ź╚╣Įļ]ż╦żĘżŲżżżļ┼└żŌ╣ŌÅ]▓Įż╦┤¾═┐żĘżŲżżżļĪŻ

▓├ż©żŲĮ±żŁ╣■ż▀┬č└ŁĪ╩ź©ź¾źŪźÕźóźķź¾ź╣Ī╦ż“äė▓ĮżĘż┐ż┐żßĪóÆņȧĄĪż╬źųźķź├ź»ź▄ź├ź»ź╣żõźėźŪź¬┤Ų£åź½źßźķż╬żĶż”ż╦Į±żŁ╣■ż▀ż╬¾Hżż├ō²ŗż╦żŌ╗╚ż©żļĪŻźŌźąźżźļ├ō²ŗżŪżŽĪóźßź┐źļź▓Ī╝ź╚╣Įļ]ż╦żĶż├żŲĪó└Łē”ż¼15%╣ŌÅ]ż╦ż╩ż├ż┐ż┐żßĪóź©ź├źĖź│ź¾źįźÕĪ╝źŲźŻź¾ź░żõAI┐õébĪóźĻźóźļź┐źżźÓż╬ź░źķźšźŻź├ź»ź╣ź▓Ī╝źÓĄĪ▀_ż╩ż╔ż╦Ė■ż»ż╚żĘżŲżżżļĪŻ

176┴žż╬NANDźšźķź├źĘźÕżŽĪóźĘź¾ź¼ź▌Ī╝źļż╬╬╠ŠÅ╣®Šņż½żķźĄź¾źūźļĮą▓┘├µżŪżóżļĪŻż│ż╬Č\Įčż“╗╚ż├ż┐żĄżķż╦┐ʿʿż×æē俎Īó2021ŃQ├µż╦Įą▓┘ż╣żļ═Į─Ļż└ż╚żżż”ĪŻ

╗▓╣═½@╬┴

1. Micron Ships WorldĪŪs First 176-Layer NAND, Delivering A Breakthrough in Flash Memory Performance and Density (2020/11/09)