IntelĪóźąź¾ź╔╔²512GB/sż╬HBM2ż“ĮĖ└čżĘż┐FPGAż“╚»Ūõ

IntelżŽĪóźąź¾ź╔╔²ż¼512Gźąźżź╚/╔├ż╚Č╦żßżŲ╣ŁżżHBM2Ī╩High Bandwidth MemoryĪ╦ż“┼ļ║▄żĘż┐FPGAĪųStratix 10 MXĪūż╬╚╬Ūõż“│½╗ŽżĘż┐ĪŻHBMżŽTSVĪ╩Through Silicon ViaĪ╦ż“╗╚ż├żŲĪóDRAMźßźŌźĻźóźņźżź┴ź├źūż“āeż╦─_ż═ż┐╣Įļ]ż“Ęeż─╣Ō╠®┼┘źßźŌźĻĪŻĮj╬╠ż╬źŪĪ╝ź┐ż“▐kĄżż╦╬«ż╣├ō²ŗż╦┼¼żĘżŲżżżļĪŻ

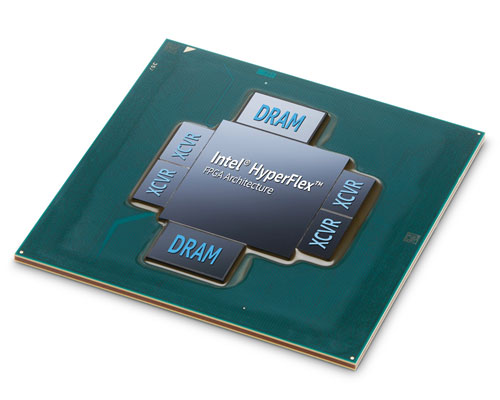

┐▐1ĪĪHBM2ż“┤łż╦ĮĖ└čżĘż┐FPGAĪóStratix 10 MXĪĪĮąųZĪ¦Intel Corp.

IntelżŽż│żņż▐żŪżŌFPGAż╬Stratix 10źšźĪź▀źĻż“Įą▓┘żĘżŲżŁż┐ĪŻ28Gbpsż╬ź╚źķź¾źĘĪ╝źąż“Ęeż─Stratix 10 GXżõĪó┴╚ż▀╣■ż▀ź»ź’ź├ź╔ź│źóż╬ArmźūźĒź╗ź├źĄż“ŲŌē┼żĘż┐Stratix 10 SXż╩ż╔ż¼żóżļĪŻ║ŻövżŽ╣ŌÅ]ż╬HBMż“┤łż╦┼ļ║▄żĘż┐FPGAż╚żżż”░╠Åøż┼ż▒żŪĪóHBMż╬źąź¾ź╔╔²żŽ╬Ńż©żą“£═Ķż╬DDR 2400 DIMMźŌźĖźÕĪ╝źļż╚╚µż┘żļż╚10Ū▄╣ŌÅ]ż└ż╚żĘżŲżżżļĪŻ

┐Ę×æēäż╬512GB/sż╚żżż”źąź¾ź╔╔²ż“Ö┌ż½ż╣├ō²ŗż╦żŽĪóHPCĪ╩╣Ō└Łē”ź│ź¾źįźÕĪ╝źŲźŻź¾ź░Īó═ūżŽź╣Ī╝źčĪ╝ź│ź¾źįźÕĪ╝ź┐żõ«ĆĮjĘ┐ź│ź¾źįźÕĪ╝ź┐Ī╦Ė■ż▒ż╬¾HĄĪē”źóź»ź╗źķźņĪ╝ź┐żõźŪĪ╝ź┐ź╗ź¾ź┐Ī╝ĪóNFVĪ╩ź═ź├ź╚ź’Ī╝ź»ĄĪē”ż╬▓Š„[▓ĮĪ╦Īó╩³┴„ż╩ż╔ż¼żóżļĪŻż│żņżķżŽĮj╬╠ż╬źŪĪ╝ź┐ż“┼Š┴„ż╣żļźŽĪ╝ź╔ź”ź©źóźóź»ź╗źķźņĪ╝ź┐żõĪóź╣ź╚źĻĪ╝źÓźŪĪ╝ź┐ż╬źčźżźūźķźżź¾Ų░║Ņż╬╗┼┴╚ż▀ż╩ż╔ż¼ØŁ═ūż╚ż╩żļĪŻ

HPC╩¼╠ŅżŪżŽĪóĮj╬╠ż╬źŪĪ╝ź┐ż“╬«ż╣ØiĖÕż╦░ĄĮ╠Ī”äP─╣ż╣żļē”╬üż¼║ŪĮjĖ┬ĄßżßżķżņżļĪŻHBM2ŲŌē┼ż╬FPGAżŽĪóFPGA├▒Ų╚żĶżĻżŌĮj╬╠ż╬źŪĪ╝ź┐┼Š┴„ż“░ĄĮ╠żĘźóź»ź╗źķźņĪ╝źĘźńź¾ż╣żļĪŻHPDAĪ╩High Performance Data AnalyticsĪ╦┤─ČŁżŪżŽĪóApache KafkażõApache Spark Streamingż╬żĶż”ż╩ź╣ź╚źĻĪ╝ź▀ź¾ź░źŪĪ╝ź┐ż╬źčźżźūźķźżź¾źšźņĪ╝źÓź’Ī╝ź»ż╦ĪóźĻźóźļź┐źżźÓż╬źŽĪ╝ź╔ź”ź©źóźóź»ź╗źķźņĪ╝źĘźńź¾ż¼ØŁ═ūĪŻStratix 10 MX FPGAżŽĪóź█ź╣ź╚CPUż╬╔ķ▓┘ż“ż½ż▒żļż│ż╚ż╩ż»ĪóźŪĪ╝ź┐ż╬Ų╔ż▀ĮążĘ/Į±żŁ╣■ż▀żõ░┼ęÄ▓Į/▓“Ų╔ż“źĻźóźļź┐źżźÓżŪŲ▒╗■ż╦╣įż©żļĪŻ

Stratix 10 MX FPGAźšźĪź▀źĻżŽĪóŪ█└■ź┴ź├źūż“┤łż╦ŲŌē┼żĘż┐Č\ĮčEMIBĪ╩Embedded Multi-Die Interconnect BridgeĪ╦ż“╗╚ż├żŲż¬żĻĪóFPGAż╚DRAMŗ╩¼ż“╣ŌÅ]▓ĮżĘżŲżżżļĪŻEMIBČ\Į迎Īó“£═Ķż╬źĘźĻź│ź¾źżź¾ź┐Ī╝ź▌Ī╝źČż“ź┴ź├źūµ£öüż╬▓╝ż╦Åøż»ż╬żŪżŽż╩ż»Īó┤łŲŌŗż╦▒·ŗż“║ŅżĻĪóż│ż╬▒·ŗż╦Ū█└■├ōż╬źĘźĻź│ź¾¾H┴žŪ█└■ź┴ź├źūż“ļmżß╣■żÓČ\ĮčżŪżóżļĪ╩┐▐2Ī╦ĪŻźĘźĻź│ź¾źżź¾ź┐Ī╝ź▌Ī╝źČż╚╚µż┘ĪóŠ«żĄż╩Ū█└■ź┴ź├źūż“╗╚ż”ż┐żßź┴ź├źū┤ųż╬š{▀`ż“ø]ż»żŪżŁżļæųż╦ź│ź╣ź╚┼¬ż╦żŽŖW▓┴ż╦ż╩żļĪŻFPGAż╚DRAM┤ųż“ż─ż╩ż░ż┐żßż╦ż│ż╬Ū█└■ź┴ź├źūż¼ļmżß╣■ż▐żņĪóżĮż╬š{▀`ż¼ø]żżż┐żßż╦╣ŌÅ]ż╦─╠┐«żŪżŁżļĪŻ║Żövż╬Č\ĮčżŪżŽHBM2żŽ┤łæųż╦ź▐źżź»źĒźąź¾źūż“─╠żĘżŲ└▀ÅøĪ”└▄¶öżĄżņĪóļmżß╣■ż▀Ū█└■ź┴ź├źūż“─╠żĘżŲFPGAż╚└▄¶öż╣żļĪŻ

┐▐2ĪĪIntelż¼│½╚»żĘż┐ź┴ź├źūļmżß╣■ż▀┤łČ\ĮčEMIBĪĪĮąųZĪ¦Intel Corp.

EMIBČ\Į迎Īó╣Ō└Łē”ż╩źŌź╬źĻźĘź├ź»FPGAż╚HBM2ż“Ė·╬©żĶż»┤łæųż╦ĮĖ└čżĘĪóźßźŌźĻźąź¾ź╔╔²ż╬ź▄ź╚źļź═ź├ź»ż“▓“Š├żĘĪóŠ├õJ┼┼╬üż“æųż▓ż║ż╦╣ŌÅ]▓Įż“├Ż└«żĘżŲżŁż┐ĪŻStratix 10 FPGAźšźĪź▀źĻżŽĪó14nm Fin FETźūźĒź╗ź╣Č\Įčż╚EMIBż╩ż╔ż╬źčź├ź▒Ī╝źĖź¾ź░Č\Įčż“ØŖ─╣ż╚żĘżŲżżżļĪŻ