XilinxĪ󟻟ķź”ź╔ĪóźėźĖźńź¾ĪóIIoTĪó5Gż╬źßź¼ź╚źņź¾ź╔ż╦×┤▒■╬ü┐āż╣

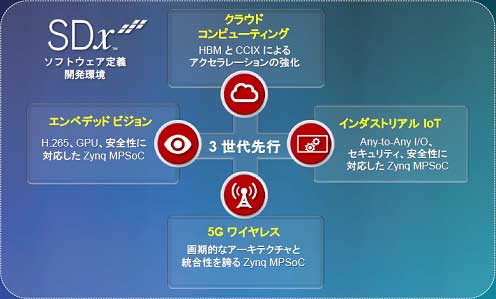

FPGAźßĪ╝ź½Ī╝ż╬Xilinxż¼ARMź│źóż╬CPUĪóGPUĪóźßźŌźĻż╩ż╔ż“ĮĖ└čżĘż┐SoCżŪżóżļĪóĪųZynqĪūż╦▓├ż©ĪóFPGAźóź»ź╗źķźņĪ╝ź┐▒■├ōż╚Č”ż╦Īó╗═ż─ż╬źßź¼ź╚źņź¾ź╔(┐▐1)ż╦×┤▒■żŪżŁżļöüöUż“┼Dż©ż┐ĪŻż╣ż╩ż’ż┴Ī󟻟ķź”ź╔ź│ź¾źįźÕĪ╝źŲźŻź¾ź░Īó┴╚ż▀╣■ż▀źėźĖźńź¾źĘź╣źŲźÓĪó╣®Č╚├ōIoTĪóżĮżĘżŲ5GźŌźąźżźļź═ź├ź╚ź’Ī╝ź»ż╦Ė■ż▒ż┐×┤▒■╬üż“┐āżĘż┐ż│ż╚ż╦ż╩żļĪŻ

┐▐1ĪĪXilinxż¼║╬żĻ╣■żÓ4ż─ż╬ź╚źņź¾ź╔ĪĪĮąųZĪ¦Xilinx

Xilinxż╬ZinqżŽĪó▐k╚╠┼¬ż╩CPUżõASICövŽ®ĪóźßźŌźĻż╦FPGAż“ĮĖ└čżĘż┐żŌż╬ĪŻCPUż“ŲŌē┼żĘżŲżżżļż┐żßźĮźšź╚ź”ź©źó×┤▒■ż¼▓─ē”ż╩ż”ż©ż╦ĪóźŽĪ╝ź╔ź”ź©źóżŪź½ź╣ź┐ź▐źżź║żĘż┐żżŠņ╣ńżŽFPGAżŪ║╣╩╠▓ĮövŽ®ż“└▀╝ŖżŪżŁżļĪŻŲ▒╝꿎ĪóśO╝ęż╬×æēäź▌Ī╝ź╚źšź®źĻź¬ż“Īųź¬Ī╝źļźūźĒź░źķź▐źųźļĪūż╚Ō}ż¾żŪżżżļĪŻż▐ż┐Īó║╣╩╠▓ĮövŽ®żõźĮźšź╚ź”ź©źóżŪŲ╚śOż╬źóźļź┤źĻź║źÓż“║ŅżļŠņ╣ńż╦źūźĒź░źķź▀ź¾ź░źŌźŪźļżŌ│½╚»ż╣żļż┐żßż╬SDxż╚Ō}żųźĮźšź╚ź”ź©źó─Ļ▒Iż╬└▀╝Ŗ┤─ČŁżŌ─¾ČĪż╣żļĪŻż│żņż╦żĶż├żŲĪóź╣ź▐Ī╝ź┐Ī╝(żĶżĻĖŁż»)Īóź│ź═ź»źŲź├ź╔Ī╩źżź¾ź┐Ī╝ź═ź├ź╚ż╚└▄¶öĪ╦Īó║╣╩╠▓Įż╬─_═ūż╩įÆż─ż╬źšźĪź»ź┐ż“Ęeż─×æēäż“║ŅżļźĄź▌Ī╝ź╚ż“╣įż”ĪŻ

╗═ż─ż╬ź╚źņź¾ź╔ż╬ŲŌĪ󟻟ķź”ź╔żŪżŽĪóź╣ź╚źņĪ╝źĖż╚ź═ź├ź╚ź’Ī╝źŁź¾ź░Īóź│ź¾źįźÕĪ╝źŲźŻź¾ź░ż“żĄżķż╦╣ŌÅ]▓Įż╣żļźóź»ź╗źķźņĪ╝ź┐ż“Ęeż─ż┐żßĪóCCIxĪ╩Cache Coherent Interconnect for AcceleratorsĪ╦źżź¾ź┐Ī╝źšź¦Ī╝ź╣ż╬╗┼══║÷─Ļż╦Ė■ż▒Īóź│ź¾źĮĪ╝źĘźóźÓż“┴╚żÓż│ż╚ż“5ĘŅż╦╚»╔ĮżĘżŲżżż┐ĪŻż│żņżŽĪóARMź│źóż╚PowerĪóX86ż╬ĘQźóĪ╝źŁźŲź»ź┴źŃż“źĄź▌Ī╝ź╚ż╣żļźżź¾ź┐Ī╝źšź¦Ī╝ź╣ż╬╗┼══żŪżóżĻĪó░█ż╩żļISAĪ╩╠┐╬ßź╗ź├ź╚źóĪ╝źŁźŲź»ź┴źŃĪ╦żŪŲ░║Ņż╣żļźūźĒź╗ź├źĄż¼źóź»ź╗źķźņĪ╝ź┐ż╚źßźŌźĻĪ╩HBMĪ╦ż“Č”Ń~żŪżŁżļżĶż”ż╦ż╣żļźĘź╣źŲźÓżŪżóżļĪŻż─ż▐żĻĪóARMźūźĒź╗ź├źĄż╚x86ĪóżóżļżżżŽź│ź░ź╦źŲźŻźųź│ź¾źįźÕĪ╝źŲźŻź¾ź░ż╬PowerźóĪ╝źŁźŲź»ź┴źŃĪóż╔ż╬źóĪ╝źŁźŲź»ź┴źŃżŪżŌźóź»ź╗źķźņĪ╝ź┐żŽŲ▒▐kźßźŌźĻż“Č”Ń~żŪżŁżļżĶż”ż╦ż╩żļĪŻź©ź│źĘź╣źŲźÓż“╣Į└«żĘżŲżżżļ(┐▐2)ĪŻ

┐▐2ĪĪCCIxźżź¾ź┐Ī╝źšź¦Ī╝ź╣ż╬ź©ź│źĘź╣źŲźÓĪĪĮąųZĪ¦Xilinx

HBMĪ╩High Bandwidth MemoryĪ╦żŽ¾H┐¶ż╬DRAMż“TSVżŪ└▄¶öżĘżŲź╣ź┐ź├ź»ż╣żļČ\ĮčżŪżóżļĪŻź»źķź”ź╔źĄĪ╝źąĪ╝żõź╣Ī╝źčĪ╝ź│ź¾źįźÕĪ╝ź┐ż╩ż╔ĪóźŪĪ╝ź┐ź╗ź¾ź┐Ī╝żŪ╗╚ż”ź│ź¾źįźÕĪ╝ź┐ż“żĄżķż╦Å]ż»ż╣żļż┐żßż╬źóź»ź╗źķźņĪ╝ź┐ż“╗╚ż”źĘź╣źŲźÓżŪżŽĪóDRAMźŌźĖźÕĪ╝źļżŽżŌżŽżõ┬ō┘I╗Ķż╦╗─żķż║ĪóHBMżŪ╣ŌÅ]▓Įż╣żļż│ż╚żŪI/Oż╬ź▄ź╚źļź═ź├ź»ż“▓“Š├ż╣żļ(┐▐3)ĪŻTSVż╬ØŖ─╣ż“║ŪżŌÖ┌ż½ż╗żļ▒■├ōż╚ż╩żļĪŻ

┐▐3ĪĪFPGAż╦HBM3╝ĪĖĄźßźŌźĻż“┼ļ║▄żĘż┐źĘź╣źŲźÓĪĪĮąųZĪ¦Xilinx

źóź»ź╗źķźņĪ╝ź┐żŽĪóCPUżžż╬╔ķ├┤ż“žōżķż╣ż┐żßż╦└▀ż▒żļ▒ķōQ└ņ├ōż╬övŽ®żŪżóżļż¼ĪóFPGAżŪ║Ņ×æż╣żņżąĪóCPUż╬ź┐ź╣ź»ż½żķŲ╚╬®żĘżŲżżżļż┐żßĪóCPUż╬╔ķ▓┘ż“ż½ż▒ż║ż╦źĘź╣źŲźÓż“╣ŌÅ]▓ĮżŪżŁżļĪŻźŪĪ╝ź┐ź╗ź¾ź┐Ī╝żŪżŽźóź»ź╗źķźņĪ╝ź┐ż╚żĘżŲFPGAż“╗╚ż”ź▒Ī╝ź╣ż¼╗\ż©żŲżżżļĪŻXilinxż╦żĶżļż╚Īó└ż─cż╬ź╚ź├źū7ĮjĮjæä╠Žż╬źŪĪ╝ź┐ź╗ź¾ź┐Ī╝ż╬ŲŌĪó3╝ęż¼║╬├ōżĘĪó2╝ęż¼äh▓┴├µż└ż╚żĘżŲżżżļĪŻ

źŪĪ╝ź┐ź╗ź¾ź┐Ī╝├ōż╬źóź»ź╗źķźņĪ╝ź┐żõGPUż╩ż╔ĪóCPUż“▌öż”Ę┴ż╬źūźĒź╗ź├źĄżŽCPUż╚źßźŌźĻż“Č”Ń~żĘżŲżżż╩ż▒żņżąĪ󟣟џ├źĘźÕż╚żĘżŲż╬źęź├ź╚╬©ż¼▓╝ż¼żĻ▒ķōQÅ]┼┘żŽż░ż├ż╚═Ņż┴żŲżĘż▐ż”ĪŻż│ż╬ż┐żßĪóCCIxżŽź¬Ī╝źūź¾ż╩┴╚“Eż└ż¼Īó└▀╬®żĄżņżļØiż╦IBMżŽPower 8ż“╗╚ż├ż┐Ų▒══ż╩źßźŌźĻČ”Ń~ż╬ż┐żßż╬CAPIĪónVidiażŽNVLinkźżź¾ź┐Ī╝ź│ź═ź»ź╚ż╚żżż”źūźĒź╚ź│źļż“├ō┴TżĘżŲżżż┐(╗▓╣═½@╬┴1)ĪŻXilinxżŽCAPIżŌźĄź▌Ī╝ź╚ż╣żļż╚Įęż┘żŲżżżļĪŻ

XilinxżŽĪóFPGAż└ż▒żŪżŽż╩ż»ĪóCPUżõźßźŌźĻGPUĪóFPGAövŽ®ż“ĮĖ└čżĘż┐SoCż╦żŌ╬üż“Ų■żņżŲżżż»ĪŻ▒ķōQ╝ńöüż╬źóź»ź╗źķźņĪ╝ź┐żŪżŽFPGAżŪ└ņ├ō▒ķōQ▀_ż╦Ė■ż▒żļż¼ĪóżĮżņ░╩│░ż╬ź╚źņź¾ź╔ĪóźėźĖźńź¾źĘź╣źŲźÓżõIIoTĪó5GźŌźąźżźļ─╠┐«ź═ź├ź╚ź’Ī╝ź»żŪżŽĪóŲ▒╝ęż╬┬Õ╔Į┼¬ż╩SoCżŪżóżļZynqż╦╬üż“Ų■żņżļĪŻźėźĖźńź¾źĘź╣źŲźÓżŽĪ󟻟ļź▐żõ╣®Šņż╩ż╔żŪرöüż“Ū¦╝▒żĘĪó╩¼└Žż╣żļż┐żßż╦CPUż╚FPGAż“ŠW├ōż╣żļż└ż▒żŪżŽż╩ż»Īó¾H┐¶ż╬źżźßĪ╝źĖź╗ź¾źĄż“┼²╣ńż╣żļź╗ź¾źĄźšźÕĪ╝źĖźńź¾(ź╗ź¾źĄźŽźųż╚żŌżżż”)ż╦żŌ╗╚ż”ĪŻ

IIoTżŪżŽĪó╣®Šņż╬Ö┌ŠÅĖ·╬©Īó╚¶╣įĄĪż╬£\╬┴õJż╬£I╠¾ż╩ż╔ż╬ų`┼¬żŪIoTż“ŠW├ōżĘĪóźĻźóźļź┐źżźÓżŪźŪĪ╝ź┐▓“└ŽżĘĪóĖ▄Ąęż╬▓┴├═ż“┴Žļ]ż╣żļĪŻ╬Ńż©żąĪóFPGAövŽ®żŪź╗ź¾źĄźšźÕĪ╝źĖźńź¾ż“╣Į└«żĘĪóźŪĪ╝ź┐▓“└ŽżŽARMź│źóżŪ╣įż”ĪŻżĄżķż╦ŖWµ£└Łż╚ź╗źŁźÕźĻźŲźŻżŌ│╬╩▌ż╣żļż┐żßż╬övŽ®żŌŲŌē┼ż╣żļĪŻ

5Gż╬─╠┐«źĘź╣źŲźÓżŪżŽĪóźŪĪ╝ź┐źņĪ╝ź╚ż╬╣ŌÅ]▓Į(║ŪĮj10Gbps)ż└ż▒żŪżŽż╩ż»Īó─ŃęÆūā(źņźżźŲź¾źĘ1ms)ĪóżĮżĘżŲ─ŃŠ├õJ┼┼╬üĪóż╚żżż”═ūĄß└Łē”ż¼żóżļĪŻZynqż╬żĶż”ż╩CPUż╚FPGAżŪĪóżĮżņżŠżņźĮźšź╚ź”ź©źóĪóźŽĪ╝ź╔ź”ź©źóżŪ═ūĄß└Łē”ż“╝┬ĖĮżĘżŲżżż»ĪŻ5Gź’źżźõźņź╣źĘź╣źŲźÓż╬╗Ņ║Ņż╦żŽż╣żŪż╦FPGAż¼¾H├ōżĄżņżŲżżżļĪŻ5GżŽż▐ż└æä│╩ż¼╬«Ų░┼¬żŪżóżļæųż╦ĪóĘQ╣±ż╬ß×═Ų╝■āS┐¶┬ė░Ķż¼źąźķźąźķżŪżóżļż┐żßĪóFPGAżŪżŌCPUżŪżŌźšźņźŁźĘźųźļż╦×┤▒■żŪżŁżļĪŻ

╚ŠŲ│öüźūźĒź╗ź╣ż╚żĘżŲż╬źżź¾źčź»ź╚żŽĪóż│żņżķż╬4Įjź╚źņź¾ź╔ż╬┬Šż╦żóżļĪŻXilinxżŽ10nmż“ź╣źŁź├źūżĘżŲżżżŁż╩żĻ7nmźūźĒź╗ź╣ż╦╚¶żųż╚żżż”ĪŻXilinx×æē俎Īó28nmż½żķ20nmĪó16nmżžż╚╝┬└ėż“└čż¾żŪżŁż┐ż¼Īóż│ż╬ĖÕżŽ10nmżž╣įż½ż║ż╦7nmżžżżż»ĪŻ×æļ]żŽżŌż┴żĒż¾ĪóTSMCż¼├┤┼÷ż╣żļĪŻ

╗▓╣═½@╬┴

1. Chip Upstarts Get Coherent with Hybrid Compute, The Next Platform (2016/05/23)