Intelż╚MicronĪ󟻟Ēź╣ź▌źżź¾ź╚Ę┐╔įĦ╚»└ŁźßźŌźĻż“źĄź¾źūźļĮą▓┘żž

Intelż╚Micron technologyżŽČ”Ų▒żŪĪóDRAMż╚NANDźšźķź├źĘźÕż“ż─ż╩ż░┐ĘĘ┐źßźŌźĻż“│½╚»żĘż┐(┐▐1)ĪŻ3D XPointĪ╩ź╣źĻĪ╝źŪźŻĪ╝ź»źĒź╣ź▌ź¾ź╚ż╚Ō}żųĪ╦Č\Įčż╚ć@¤²ż▒ż┐ż│ż╬╔įĦ╚»└ŁźßźŌźĻżŽĪóź╣ź╚źņĪ╝źĖź»źķź╣źßźŌźĻżŪżóżļĪŻNANDżĶżĻżŌ3ź▒ź┐Å]ż»ĪóDRAMżĶżĻżŌ10Ū▄╣Ō╠®┼┘żŪĪóNANDżĶżĻżŌĮ±żŁ┤╣ż©öv┐¶ż¼1000Ū▄¾Hżżż╚żżż”ĪŻ

┐▐1ĪĪ3D XPointźŲź»ź╬źĒźĖĪ╝ż“╗╚ż├ż┐128Gźėź├ź╚ż╬źßźŌźĻ

ĮąųZĪ¦IntelĪóMicron Technology

ż│ż╬żĶż”ż╩ź╣ź╚źņĪ╝źĖź»źķź╣źßźŌźĻżŽĪóDRAMż╚NANDźšźķź├źĘźÕż╬żĶż”ż╩ź╣ź╚źņĪ╝źĖźŪźąźżź╣ż“ļmżßżļż┐żßż╬źßźŌźĻżŪżóżļĪŻż│żņż▐żŪż╬ź│ź¾źįźÕĪ╝ź┐źóĪ╝źŁźŲź»ź┴źŃżŪżŽĪóźūźĒź╗ź├źĄż╚źŪĪ╝ź┐ż“└õż©ż║żõżĻŲDżĻż╣żļDRAMżŽĪó╦▄┼÷żŽĮj═Ų╬╠ż“┴╚żÓż│ż╚żŪź│ź¾źįźÕĪ╝ź┐źĘź╣źŲźÓż“╣ŌÅ]▓ĮżŪżŁżļż¼ĪóźĘź╣źŲźÓż¼╣Ō▓┴ż╦ż╩ż├żŲżĘż▐ż”ĪŻżĘż½żĘĪóDRAM═Ų╬╠ż¼Ė┬żķżņżŲżżżļż╚ĪóźūźĒź╗ź├źĄżŽź╣ź╚źņĪ╝źĖż╚żõżĻŲDżĻż╗żČżļż“įuż╩ż»ż╩żĻĪóźóź»ź╗ź╣żŽØÖŠ’ż╦ęÆż»ż╩żļĪŻż│ż╬ż┐żßĪóDRAMż╚ź╣ź╚źņĪ╝źĖż“ż─ż╩ż░ŖW▓┴ż╩źßźŌźĻż¼ĄßżßżķżņżŲżżżļĪŻ

ĖĮ║▀ż╬NANDźšźķź├źĘźÕż╩żķĪóźņźżźŲź¾źĘżŽ┐¶Ø▓”╠sż╚ęÆżżż¼Īóż│ż╬┐ĘĘ┐źßźŌźĻżŪżŽ┐¶Ø▓nsż╚NANDżĶżĻżŌ3ź▒ź┐Å]żżĪŻż│ż╬ż┐żßĪóDRAMż╚NANDźšźķź├źĘźÕż╚ż╬┤ųż╬Å]┼┘ź«źŃź├źūż“ļmżßżļż│ż╚ż¼żŪżŁżļĪŻżŌż┴żĒż¾ĪóNANDźšźķź├źĘźÕżŪżĄż©ĪóHDD(źŽĪ╝ź╔ź╔źķźżźų)ż╚╚µż┘żļż╚3ź▒ź┐╣ŌÅ]ż└ż½żķĪóź╣ź╚źņĪ╝źĖźŪźąźżź╣żŽ▐k╚╠ż╦HDDż½żķNANDźšźķź├źĘźÕźóźņźżżžöĪ╣įżĘż─ż─żóżļĪŻ║Żövż╬3D XPointźßźŌźĻżŽHDDżĶżĻżŌ6ź▒ź┐Å]ż»ż╩żļĪŻ

╣ŌÅ]żŪŖW▓┴ż╩ź╣ź╚źņĪ╝źĖź»źķź╣źßźŌźĻż¼żŪżŁżļżĶż”ż╦ż╩żļż╚ĪóźŪĪ╝ź┐ż“┐¶Ø▓nsżŪźóź»ź╗ź╣żŪżŁżļżĶż”ż╦ż╩żĻĪó╬Ńż©żąŠ«ŪõżĻČ╚ŪvżŽĪóŠ”ēäż╚ż╬ŲD░·żŪż╬ĄČż╬IDźčź┐Ī╝ź¾ż“║t║┬ż╦Ė½Ū╦żļż│ż╚ż¼żŪżŁżļĪŻźžźļź╣ź▒źóĖ”ē|ŪvżŽĪó╦─Įjż╩źŪĪ╝ź┐ż“źĻźóźļź┐źżźÓżŪĮĶ═²Ī”▓“└ŽżŪżŁżļżĶż”ż╦ż╩żĻĪóŅC┼┴╗ę▓“└Žżõ┼┴ģ¢Ļāż╬╝{└ūż╩ż╔ż¼╣ŌÅ]ż╦żŪżŁżļżĶż”ż╦ż╩żļĪŻ

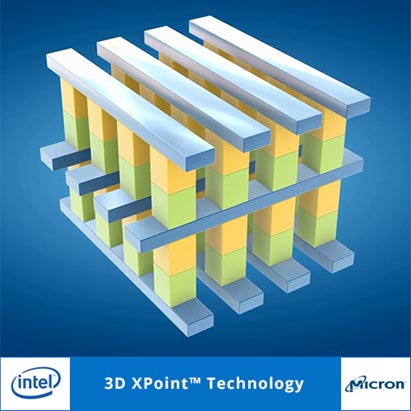

┐▐2ĪĪź»źĒź╣ź▌źżź¾ź╚źóĪ╝źŁźŲź»ź┴źŃż╬3D XPointźßźŌźĻĪĪĮąųZĪ¦IntelĪóMicron

źßźŌźĻ╣Įļ]żŽź»źĒź╣ź▌źżź¾ź╚źóźņźż╣Įļ]żŪĪó┐▐2ż╬ź¬źņź¾źĖŗ╩¼ż“┬ō┘IźŪźąźżź╣Īó£uŗ╩¼ż“źßźŌźĻź╗źļż╚żĘżŲ╗╚ż”ĪŻź╚źķź¾źĖź╣ź┐źņź╣ż└ż╚żĘżŲżżżļĪŻ┬ō┘IźŪźąźżź╣ĪóźßźŌźĻź╗źļż╚żŌż╔ż╬żĶż”ż╩║Ó╬┴żŪżŪżŁżŲż¬żĻĪóż╔ż╬żĶż”ż╩ĖČ═²żŪŲ░║Ņż╣żļż╬ż½ż╦ż─żżżŲżŽ£½żķż½ż╦żĘżŲżżż╩żżĪŻPCRAMż½STT-MRAMż½żĄż©Īó£½ż½żĘżŲżżż╩żżĪŻ

źóź»ź╗ź╣ż╣żļŠņ╣ńżŽĪóæųż╬ź’Ī╝ź╔└■ż╚▓╝ż╬źėź├ź╚└■ż╦┼┼░Ąż“ż½ż▒ź¬źņź¾źĖ┐¦ż╬┬ō┘IźŪźąźżź╣ż“─╠żĘżŲźßźŌźĻź╗źļż╦Į±żŁ╣■ż▀Ų╔ż▀ĮążĘż╣żļĪŻż│ż╬ź»źĒź╣ź▌źżź¾ź╚źóźņźżżŽĪó┐▐2ż╬żĶż”ż╦źóźņźżĀCż“2├╩ż╦└čż▀─_ż═żŲ═Ų╬╠ż“╗\żõż╣ż│ż╚ż¼żŪżŁżļĪŻDRAMżŪżŽź╚źķź¾źĖź╣ź┐ż“źßźŌźĻź╗źļż╬▓Żż╦Ū█ÅøżĘżŲżżż┐ż¼Īó3D XPointżŪżŽź╚źķź¾źĖź╣ź┐żŽż╩ż»Īó┬ō┘IźŪźąźżź╣ż“źßźŌźĻź╗źļż╦āe└čż▀żŪżŁżļż┐żßĪóźßźŌźĻ═Ų╬╠ż“DRAMż╬10Ū▄ż╦żŪżŁżļż╚żżż”ĪŻ

ż╣żŪż╦ĖĮ║▀╬╠ŠÅ▓─ē”ż╩źūźĒź╗ź╣Č\ĮčżŪĪó128Gźėź├ź╚ż╬╗Ņ║Ņēäż“Ö┌ŠÅżĘżŲż¬żĻĪó║ŻŃQż╬ĖÕ╚Šż╦żŽźĄź¾źūźļĮą▓┘ż“╗Žżßżļ═Į─Ļż└ĪŻż│ż╬Č\Į迎IntelĪóMicronż½żķżĮżņżŠżņ×æēäż╚żĘżŲ╚╬Ūõż╣żļż│ż╚ż╦ż╩żļĪŻ