Tabula╝ęĪóFPGAČ\ĮčżŪ─╠┐«├ōASSPż“×æēä▓ĮĪóźūźĒź░źķźÓżŌ▓─ē”ż╦

źĒźĖź├ź»övŽ®ż“╗■╩¼│õż╦Ņ~Ų░żĘżŲŠ«żĄż╩ź┴ź├źūżŪĮj(lu©░)æä╠ŽFPGA┴Ļ┼÷ż╬źĒźĖź├ź»ż“╝┬ĖĮż╣żļä▌╣±ż╬ź┘ź¾ź┴źŃĪ╝Tabula╝ęż¼Intelż╬22nm FINFETźūźĒź╗ź╣ż“╗╚żż100Gbpsź»źķź╣ż╬×æēäż“3ēä¹|│½╚»żĘż┐ĪŻ100Gbpsż╬źżĪ╝źĄź═ź├ź╚źųźĻź├źĖźšźĪź▀źĻż╚4ź┴źŃź¾ź═źļż╬100GigEź╣źżź├ź┴Īó40Gbpsż╬źņź«źÕźķĪ╝ź©ź»ź╣źūźņź├źĘźńź¾Ī╩┘ćæä╔ĮĖĮĪ╦źóź»ź╗źķźņĪ╝ź┐ż╬įÆż─ĪŻ

Tabulaż╬FPGAżŽĪóSpacetimeż╚Ō}żų╗■╩¼│õżŪźĒźĖź├ź»ż“Į±żŁ┤╣ż©żŲżżż»öĄ(sh©┤)╝░ż╬źóĪ╝źŁźŲź»ź┴źŃĪŻXilinxżõAlteraż╬FPGAż└ż╚ź┴ź├źūż¼Įj(lu©░)żŁż»ż╩ż├żŲżĘż▐ż”ż╬ż╦×┤żĘżŲĪóŠ«żĄż╩ź┴ź├źūźĄźżź║żŪŲ▒┼∙ż╬źĒźĖź├ź»źĄźżź║ż“╝┬ĖĮż╣żļż┐żßż╦╗■╩¼│õżŪĪóźĒźĖź├ź»ż“Į±żŁ┤╣ż©żŲżżż»ĪŻ╗■╣’Taż▐żŪźņźżźõĪ╝1ż╬źĒźĖź├ź»ĪóTaż½żķTbż▐żŪżŽźņźżźõĪ╝2ż╬źĒźĖź├ź»Īóż╚żżż”É║╣ńż╦źĒźĖź├ź»ż“╗■╩¼│õżŪ╝ĪĪ╣ż╚╣Į└«Ī”ź╣ź╚źóĪ”Š├ĄŅĪ”║Ų╣Į└«ż“Ę½żĻ╩ųżĘżŲżżż»ĪŻźņźżźõĪ╝ż“└┌żĻü÷ż©żŲżżż»╗■┤ųżŽ┐¶psż╚ø]ż»ĪóźļĪ╝ź┐ż“╗╚żżöUĖµż╣żļĪŻ

┐▐1ĪĪTabula╝ęCMOĘ¾źĘź╦źóźąźżź╣źūźņźĖźŪź¾ź╚ż╬Alain BismuthĢ■

ż│ż╬Ų╚ØŖż╩źĒźĖź├ź»źóĪ╝źŁźŲź»ź┴źŃż“│½╚»żĘż┐TabulażŽĪóż│ż╬ż█ż╔FPGA×æēäż╚żżż”żĶżĻżŌASSPż╚Ō}żųż┘żŁ╣ŌÅ]ż╬─╠┐«źčź▒ź├ź╚ĮĶ═²ż╬źĮźĻźÕĪ╝źĘźńź¾ż╦źšź®Ī╝ź½ź╣żĘżŲżżż»ĪŻįÆż─ż╬×æēäĘ▓żŽĪóż│ż╬ż▐ż▐żŪżŌ╗╚ż©żļASSPżŪżóżļż¼ĪŻźµĪ╝źČĪ╝źĒźĖź├ź»żŌżóżĻĪó╔w─ĻżĘż┐─╠┐«├ōASSPżŽĪųźĒźĖź├ź»ż╬20%µć┼┘żĘż½╗╚ż├żŲżżż╩żżż┐żßĪóFPGAżŪź½ź╣ź┐ź▐źżź║żŌżŌż┴żĒż¾żŪżŁżļĪūż╚Ų▒╝ęCMOżŪźĘź╦źóźąźżź╣źūźņźĖźŪź¾ź╚ż╬Alain BismuthĢ■(┐▐1)żŽżżż”ĪŻ

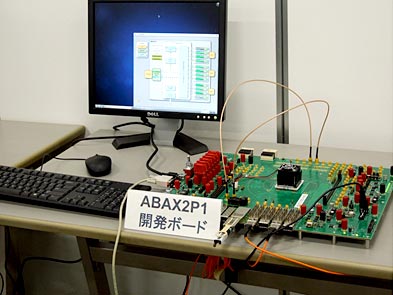

┐▐2ĪĪź╣źżź├ź┴│½╚»ź▄Ī╝ź╔

ż│żņżķż╬×æēäż“Šę▓ż╣żļĪŻż▐ż║Īó100Gbpsż╬źżĪ╝źĄź═ź├ź╚źųźĻź├źĖżŽĪó12ź┴źŃź¾ź═źļĪ▀10Gźėź├ź╚/╔├ż╬┐«ęÄ(gu©®)ż“100Gbpsż╬źĘźĻźóźļ┐«ęÄ(gu©®)ż╦╩č┤╣żĘĪóżĮż╬ĄšżŌ╣įż”ĪŻż│ż╬ABAX2P1ź┴ź├źūż“╗╚żżĪóź╣źżź├ź┴│½╚»ź▄Ī╝ź╔(┐▐2)ż“─¾ČĪż╣żļĪŻż│ż╬ź┴ź├źūżŽĪó100Gbpsż╬╝Ī└ż┬ÕźļĪ╝ź┐żõźŪĪ╝ź┐ź╗ź¾ź┐Ī╝Ė■ż▒ż╬ź╣źżź├ź┴├ōż“┴└ż├żŲżżżļĪŻ100Gbpsż╚Č╦żßżŲ╣ŌÅ]ż╦źėźŪź¬ż╩ż╔ż╬┐«ęÄ(gu©®)ż“┴„£p┐«ż╣żļ├ō²ŗżŪżŽĪóĖ„┼┴┴„ż¼ØŁ┐▄ż╦ż╩żļĪŻż│ż╬ż┐żßĪóIntelż¼│½╚»żĘż┐źĘźĻź│ź¾źšź®ź╚ź╦ź»ź╣Č\Įčż╦żĶżļĖ„źšźĪźżźą┴„£p┐«źŌźĖźÕĪ╝źļĪ╩┐▐3Ī╦ż“ŠW(w©Żng)├ōż╣żļĪŻĖ„źšźĪźżźążŽ─╣żĄ300mż▐żŪźĄź▌Ī╝ź╚ż╣żļĪŻ

┐▐3ĪĪIntelż¼│½╚»żĘż┐┴„£p┐«Ė„źšźĪźżźąźŌźĖźÕĪ╝źļĪĪźĘźĻź│ź¾źšź®ź╚ź╦ź»ź╣Č\Įčż“ŠW(w©Żng)├ō

Ų¾ż─ų`ż╬×æē俎Īó100Gbpsż╬┐«ęÄ(gu©®)ż“4ź┴źŃź¾ź═źļ╩¼ź╣źżź├ź┴ż╣żļźĘź¾ź░źļź┴ź├źūż╬×æēäĪŻż│żņżŌABAXP1źĮźĻźÕĪ╝źĘźńź¾ż“źūźĒź░źķźÓżĘżŲASSP┼¬ż╩ź╣źżź├ź┴×æēäż╦╗┼æųż▓ż┐żŌż╬ĪŻż│żņżŽźšźņĪ╝źÓ├▒░╠żŪ─╠┐«ż╬┴T╠Żż“Ęeż─źņźżźõĪ╝2ż½żķLANŲ▒╗╬ż╬ź╣źżź├ź┴öUĖµż“╣įż”źņźżźõĪ╝3Ī󿥿ķż╦TCP/UDPźžź├ź└ż╬ź▌Ī╝ź╚╚ųęÄ(gu©®)ż“ĖĄż╦źčź▒ź├ź╚ż╬╬«żņż“öUĖµż╣żļźņźżźõĪ╝4ż╬ź╣źżź├ź┴ż╦╗Ļżļ▐kŽóż╬ź╣źżź├ź┴ż“źĄź▌Ī╝ź╚ż╣żļĪŻĘQ100Gbpsż“┴„£p┐«ż╣żļź▌Ī╝ź╚ż“4Ė─Ęeż┴Īóź▌Ī╝ź╚┤ųż╬źņźżźŲź¾źĘżŽ500nsż╚ø]żżĪŻ

įÆż─ų`ż╬×æēä40Gbpsż╬RegExĪ╩┘ćæä╔ĮĖĮĪ╦źóź»ź╗źķźņĪ╝ź┐żŽĪóź═ź├ź╚ź’Ī╝ź»ź╗źŁźÕźĻźŲźŻż╬┐┤┬Īŗż╚żżż”╠“│õż“▓╠ż┐ż╣ĪŻż│żņżŽźčź▒ź├ź╚─╣ż“ź┴ź¦ź├ź»żĘżŲ┤ØŹźčź┐Ī╝ź¾ż╚ź▐ź├ź┴ź¾ź░żĄż╗żļöĄ(sh©┤)╦Īż“╗╚ż├żŲĪ󟻟Ēź╣źčź▒ź├ź╚ż“ź┴ź¦ź├ź»ż╣żļĪŻ1Mż╬┤ØŹźļĪ╝źļż“Ęeż─ĪŻź╣źļĪ╝źūź├ź╚żŽ40GbpsĪŻż│ż╬×æē俎źčź▒ź├ź╚żõźŪĪ╝ź┐ż╬ź╣źżź├ź┴ź¾ź░ż“╣įż”║ŪĮķż╬Ų¾ż─ż╬×æēäż╚┴╚ż▀╣ńż’ż╗żŲĪóźčź▒ź├ź╚ż╬ź╗źŁźÕźĻźŲźŻż“ź┴ź¦ź├ź»ż╣żļżŌż╬ĪŻ

×æē俎įÆż─ż╚żŌźŪĪ╝ź┐ź╗ź¾ź┐Ī╝żõĮj(lu©░)żŁż╩źĄĪ╝źąż“×óż©ż┐źŪĪ╝ź┐Ė“┤╣Īóźčź▒ź├ź╚─╠┐«ż╬ź╣źżź├ź┴żõźļĪ╝ź┐ż╩ż╔ż╦╗╚├ōż╣żļźŽźżź©ź¾ź╔ż╩Š”ēäżŪżóżļĪŻĮj(lu©░)æä╠ŽFPGA┴Ļ┼÷ż╬Š«ĀC└čFPGAż╬▌xŠņż╚żĘżŲĪó─╠┐«źżź¾źšźķżõŠÅČ╚├ō²ŗż“┴└ż├żŲżżż»ĪŻ