źóźļźŲźķĪóFPGA┤ļČ╚ż½żķźĮźšź╚ż╚źĘźĻź│ź¾ż╬═╗╣ń╚ŠŲ│öü┤ļČ╚żž

źóźļźŲźķżŽĪóFPGA┤ļČ╚ż½żķ├”╚ķżĘżŲźĘźĻź│ź¾ż╚źĮźšź╚ź”ź©źóż╬═╗╣ńż╬╗■┬Õż╦żšżĄż’żĘżż┤ļČ╚ż╦ż╩żļĪóż╚┐Ę└’ŠSż“╚»╔ĮżĘż┐ĪŻŲ▒╝꿎SoC FPGAż╚Ō}żėĪóCĖ└Ėņź┘Ī╝ź╣żŪźūźĒź░źķź▀ź¾ź░ż╣żļOpenCL│½╚»ź─Ī╝źļż“┼Dż©żļż│ż╚żŪĪó28nmż½żķ20nmżžż╬öĪ╣įżŌź╣źÓĪ╝ź╣ż╦ż╩żļż╚ż╣żļĪŻ

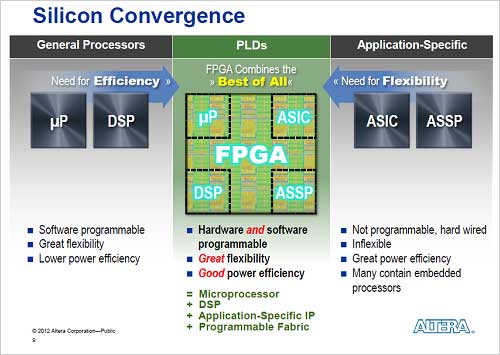

┐▐1ĪĪźĘźĻź│ź¾æųż╦źūźĒź╗ź├źĄĪóDSPĪóFPGAż╩ż╔ż“ĮĖ└čż╣żļźĘźĻź│ź¾ź│ź¾źąĪ╝źĖź¦ź¾ź╣ĪĪĮąųZĪ¦Altera

źĘźĻź│ź¾ż╚źĮźšź╚ź”ź©źóż╬═╗╣ń(ź│ź¾źąĪ╝źĖź¦ź¾ź╣)żŪżŽĪó└@├ōż╬ź▐źżź»źĒźūźĒź╗ź├źĄżõDSPż╚ĪóASICż╬żĶż”ż╩ź½ź╣ź┐źÓICż╚ż╬╣źżżż╚ż│ŲDżĻż“ż╣żļĪŻ└@├ōż╬ź▐źżź»źĒźūźĒź╗ź├źĄżŽźūźĒź░źķźÓżŪĄĪē”ż“╝{▓├żĘż┐żĻ─┤┼DżĘż┐żĻżŪżŁżļż¼Īó└Łē”żŽźŽĪ╝ź╔ź’źżźõĪ╝ź╔źĒźĖź├ź»żĶżĻ╬¶żļĪŻ▐köĄ(sh©┤)ĪóASICżŽövŽ®ż“źŽĪ╝ź╔ź”ź©źóż└ż▒żŪ┴╚ż¾żŪżżżļż┐żß└Łē”żŽ╣Ōżżż¼ĪóźšźņźŁźĘźėźĻźŲźŻżŽż╩żżĪŻźóźļźŲźķż╬ź│ź¾źąĪ╝źĖź¦ź¾ź╣ź┴ź├źūż╦żŽĪóź▐źżź»źĒźūźĒź╗ź├źĄź│źóżõDSPź│źóĪó└ņ├ōż╬╝■╩šövŽ®(┐▐Ż▒ż╬ASICŗ)ż╩ż╔ż¼ĮĖ└迥żņżŲżżżļĪŻż│ż│żŪASICż╚żóżļż╬żŽĪóPCIeżõUSB3.0ż╩ż╔ż╬╣ŌÅ]─╠┐«źżź¾ź┐Ī╝źšź¦Ī╝ź╣ż╬żĶż”ż╦»éż▐ż├ż┐övŽ®żŪżóżļĪŻH.264ż╬żĶż”ż╩źėźŪź¬ź│Ī╝źŪź├ź»żŌż│ż╬övŽ®ż╦Ų■żļĪŻ

ź▐źżź»źĒźūźĒź╗ź├źĄżõDSPżŽźĮźšź╚ź”ź©źóźūźĒź░źķź▐źųźļżŪżóżĻĪóFPGAżŽźŽĪ╝ź╔ź”ź©źóźūźĒź░źķź▐źųźļżŪżóżļĪŻź▐źżź»źĒźūźĒź╗ź├źĄżŽCĖ└ĖņżõJavaż╩ż╔żŪźūźĒź░źķźÓż╣żļż╬ż╦×┤żĘżŲĪóFPGAżŽVHDLż╩ż╔ż╬źŽĪ╝ź╔ź”ź©źóĖ└ĖņżŪźūźĒź░źķźÓżĘżŲżŁż┐ĪŻźĘźĻź│ź¾ź│ź¾źąĪ╝źĖź¦ź¾ź╣ź┴ź├źūżŪżŽĪóCĖ└ĖņżŪFPGAżŌDSPżŌźūźĒź░źķźÓżŪżŁżļżĶż”ż╦ż╣żļż┐żßOpenCLż╦ØŹĄ“ż╣żļź─Ī╝źļż“┬Ęż©ż┐ĪŻOpenCLżŽź▐źļź┴ź│źóżõźžźŲźĒźĖź╦źóź╣ż╩żĄż▐żČż▐ż╩ź│źóż“źūźĒź░źķź▀ź¾ź░ż╣żļż┐żßż╬Č”─╠ż╚ż╩żļźšźņĪ╝źÓź’Ī╝ź»żŪżóżļĪŻ

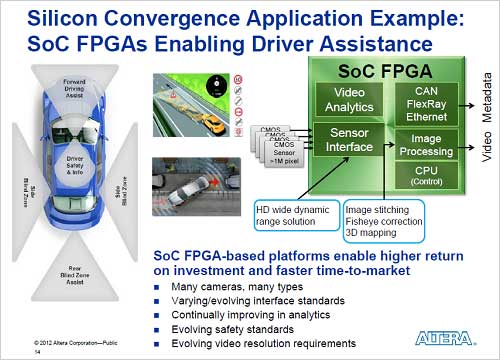

╬Ńż©żąĪóśOŲ░┘Zż╬ŖWµ£└Łż“╣Ōżßżļź╔źķźżźąÜ¦▐qźĘź╣źŲźÓ(┐▐2)żŪżŽĪó╩Ż┐¶ż╬CMOSźżźßĪ╝źĖź╗ź¾źĄź½źßźķż½żķż╬┐«ęÄ(gu©®)ż“ź╗ź¾źĄźżź¾ź┐Ī╝źšź¦Ī╝ź╣żŪ£pż▒ĪóĄ¹┤Ńźņź¾ź║ż╬T┘ćĪóرöüż╬Ū¦╝▒ż╚▓“└Žż“Ų▒╗■ż╦╣įżżĪóźėźŪź¬ĮĶ═²ż“╗▄żĘż┐ĖÕĪó▒Ū楿õźŲźŁź╣ź╚ż╩ż╔ż╬źßź┐źŪĪ╝ź┐ż“Įą╬üż╣żļĪŻż│ż”żżż├ż┐SoC FPGAżŪżŽ╩Ż┐¶ż╬źżź¾ź┐Ī╝źšź¦Ī╝ź╣Īó╩Ż┐¶ż╬ź½źßźķ┐«ęÄ(gu©®)Ų■╬üĪó╩Ż┐¶ż╬ŖWµ£æä│╩Īó╩Ż┐¶ż╬źėźŪź¬▓“ćĄ┼┘ż╩ż╔ż¼żóżĻĪóµ£żŲż“ø]╗■┤ųżŪŲ▒╗■ż╦▒ķōQżĘż╩ż▒żņżąż╩żķż╩żżĪŻż│ż”żżż├ż┐├ō²ŗżŪżŽCPUżŌDSPżŌFPGAżŌµ£żŲCĖ└ĖņżŪźūźĒź░źķźÓżŪżŁĪóČ”─╠ż╬źšźņĪ╝źÓź’Ī╝ź»żŪ╔ĮĖĮżŪżŁżņżąø]╗■┤ųżŪ└▀╝ŖżŪżŁżļĪŻ

┐▐2ĪĪź╔źķźżźąÜ¦▐qźĘź╣źŲźÓżŪżŽ╩Ż╗©ż╩źėźŪź¬ĮĶ═²ż¼╣įż’żņżŲżżżļĪĪĮąųZĪ¦Altera

ż│ż╬ź│ź¾źąĪ╝źĖź¦ź¾ź╣źĘź╣źŲźÓż╬źßźĻź├ź╚żŽ│╚─ź└Łż¼żóżļż│ż╚żŪĪó28nmż½żķ20nmżžöĪ╣įż╣żļŠņ╣ńżŪżŌŲ▒żĖ└▀╝Ŗź─Ī╝źļż¼╗╚ż©żļĪŻ2.5DżóżļżżżŽ3Dż╦ź┴ź├źūż“└č┴žż╣żļŠņ╣ńżŪżŌŲ▒══ż└ĪŻźóźļźŲźķżŽ28nmż½żķ20nmżž╚∙║┘▓Įż╣żļŠņ╣ńżŪżŌ┤╦▄╣Į└«żŽĪóARM Cortex-A9źūźĒź╗ź├źĄź│źóż“źŪźÕźóźļżŪ╗╚żżĪ󟣟џ├źĘźÕ╣Į└«żŌŲ▒══ż╬źóĪ╝źŁźŲź»ź┴źŃż“╗╚ż”ĪŻöĪ╣įż╣żļż│ż╚ż╦żĶż├żŲ└Łē”żŽ50%Ė■æųĪóŠ├õJ┼┼╬üżŽ║ŪĮj(lu©░)60%║’žō(f©┤)żĄżņĪóĮĖ└č┼┘żŽ6Ū▄╣Ōż▐żļż╚żĘżŲżżżļĪŻCortex-A15ź│źóż“╗╚ż”ØŁ═ūżŽż╩żżż╚żżż”ĪŻ20nmź┴ź├źūż╦ĮĖ└迥żņżļżŌż╬żŽĪó╬Ńż©żą40Gbpsź╚źķź¾źĘĪ╝źążõ▓─╩č╗@┼┘ż╬DSPź│źóĪ╩5 TFLOPs░╩æųż╬╔ŌŲ░Š«┐¶┼└▒ķōQ└Łē”Ī╦ĪóźžźŲźĒż╩3D ICsĪ╩FPGAż╦HardCopy ASICĪóźßźŌźĻż╩ż╔Ī╦ż╩ż╔ż“„[─ĻżĘżŲżżżļĪŻ

┐▐3ĪĪźóźļźŲźķCEOż╬John DaaneĢ■

źóźļźŲźķżŽ║“ŃQĪóŪõæų±Y20▓»6400╦³ź╔źļż╬ŲŌĪó3▓»2600╦³ź╔źļż“Ė”ē|│½╚»õJż╦╗╚ż├żŲżŁż┐ĪŻ║Żövż╬źĘźĻź│ź¾ź│ź¾źąĪ╝źĖź¦ź¾ź╣żŽż│ż”żżż├ż┐│½╚»┼Ļ½@ż“żĘż┐±T▓╠żŪżóżĻĪó┼¼┘ćż╩źĘź╣źŲźÓż╦┼¼┘ćż╩Č\Įčż“╗╚ż”╣ź╬Ńż╚ż╩ż├ż┐Īóż╚Ų▒╝ęCEOż╬John DaaneĢ■(┐▐3)żŽĖņżļĪŻ