28nmż╬FPGAżŽźżź¾ź┐ź▌Ī╝źČŠW(w©Żng)├ōżŪTbps╝┬ĖĮĪóź▐źļź┴ź│źóŲŌē┼żŪĮĶ═²+▓“└Ž├ōż╦

±śŽčż╬TSMCż¼28nmźūźĒź╗ź╣ż╬╬╠ŠÅż“│½╗ŽĪó28nmźūźĒź╗ź╣ż“ź┘Ī╝ź╣ż╦żĘż┐FPGAż“ä▌╣±ż╬źČźżźĻź¾ź»ź╣Ī╩XilinxĪ╦╝ęż╚źóźļźŲźķĪ╩AlteraĪ╦╝ęż¼żĮżņżŠżņ╚»╔ĮżĘż┐ĪŻČ”ż╦Īó28nmż╚żżż”╚∙║┘▓ĮźūźĒź╗ź╣ż╦ØŖ─╣ż¼żóżļż╬żŪżŽż╩ż»ĪóźČźżźĻź¾ź»ź╣żŽźĘźĻź│ź¾źżź¾ź┐ź▌Ī╝źČż“ŠW(w©Żng)├ōżĘż┐2.5╝ĪĖĄICż“ĪóźóźļźŲźķżŽ▒čARMż╬Cortex-A9ż╬ź▐źļź┴ź│źóż“ŲŌē┼żĘż┐Cyclone Vż╚Arria Vż“żĮżņżŠżņ╚»╔ĮżĘżŲżżżļĪŻ

TSMCż¼├ō┴TżŪżŁż┐ż╬żŽĪó28HPĪ╩high performanceĪ╦ż╚28HPLĪ╩high performance low powerĪ╦Īó28LPĪ╩low powerĪ╦Īó28HPMĪ╩high performance mobile computingĪ╦4ż─ż╬źūźĒź╗ź╣żŪżóżļĪŻżĮż╬ż”ż┴Øiż╬3ż─żŽ╬╠ŠÅ│½╗ŽżĘżŲż¬żĻĪó28HPMż╬ż▀║ŻŃQ¼Źż▐żŪż╦╬╠ŠÅż“│½╗Žż╣żļĪŻ

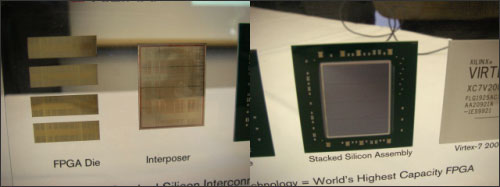

źČźżźĻź¾ź»ź╣ż╬Virtex-7 2000TżŽĪóTSMCż╬28HPLźūźĒź╗ź╣ż“ŠW(w©Żng)├ōżĘżŲżżżļĪŻż│ż╬ź┴ź├źūżŽĪóźĘźĻź│ź¾źżź¾ź┐ź▌Ī╝źČż╚FPGAź┴ź├źū4Ė─ż“TSVĪ╩through silicon viaĪ╦żŪ─_ż═╣ńż’ż╗żŲ└▄¶öĪó╣ń╝Ŗ68▓»ź╚źķź¾źĖź╣ź┐ż╦Ą┌żųICżŪżóżļĪŻFPGAź┴ź├źūż╦TSVżŪÅ──╠╣”Ī󿥿ķż╦ź▐źżź»źĒźąź¾źūż“└▀ż▒ĪóŪ█└■ŗż╚ż╩żļźĘźĻź│ź¾ż╬źżź¾ź┐ź▌Ī╝źČż╦C4źąź¾źūż“└▀ż▒ĪóżĮżņżŠżņż“└▄¶öżĘżŲżżżļĪŻż│żņż▐żŪż╚╚µż┘16Ī┴20Ū▄żŌż╬Ū█└■╠®┼┘ż╦ż╩żļĪŻFPGAź┴ź├źūŲ▒╗╬żŽ─Š└▄└▄¶öż╗ż║ĪóČ”─╠ż╬źżź¾ź┐ź▌Ī╝źČż╬æųż╦FPGAż“4š`╩┬ż┘żļĪŻźżź¾ź┐ź▌Ī╝źČż╬Ū█└■┴Ē┐¶żŽ4┴žĪŻźĒźĖź├ź»ź©źņźßź¾ź╚┐¶ż╦żĘżŲ200╦³ź©źņźßź¾ź╚ĪóASICź▓Ī╝ź╚ż╦┤╣ōQżĘżŲ2000╦³ź▓Ī╝ź╚ż╦ż╩żļĪŻŠ├õJ┼┼╬üżŽ┴╚ż▀╣ńż’ż╗övŽ®ż╦żŌżĶżļż¼20Wµć┼┘ĪŻ

źČźżźĻź¾ź»ź╣ż╦żĶżļż╚Īóż│żņż▐żŪ║ŪĮj(lu©░)æä╠Žż╬źŌź╬źĻźĘź├ź»FPGAżŽ39▓»ź╚źķź¾źĖź╣ź┐żŪ98╦³źĒźĖź├ź»ź©źņźßź¾ź╚ż└ż╚żżż”ĪŻźĒźĖź├ź»ŠW(w©Żng)├ō╬©ż“╣═╬ĖżĘżŲĄĪē”┼¬ż╦żŽ“£═Ķ║ŪĮj(lu©░)ż╬FPGAż╚żĘżŲ70╦³źĒźĖź├ź»ź©źņźßź¾ź╚ż╬FPGAż“4Ė─╗╚żżĪóŪ█└■żŪ└▄¶öż╣żļŠņ╣ńż╚Ų▒żĖĄĪē”ż“Ęeż─ż╚żĘżŲĪóŠ├õJ┼┼╬üż“Ė½└čżŌżļż╚ĪóĘQFPGAż¼20WĪóżĮżņżķż“±TżųŪ█└■ż“Ņ~Ų░ż╣żļż┐żßż╬┼┼╬üż¼8Wż╚żĘżŲĪó20WĪ▀4Ė─Ī▄8WĪ▀4Ė─Īß112Wż╚ż╩żĻĪóŠ├õJ┼┼╬üżŽ┐Ę×æēäż╬5.6Ū▄ż╦żŌ├Żż╣żļĪŻ

║ŻövźČźżźĻź¾ź»ź╣żŽĪóĄĮj(lu©░)ż╩źĒźĖź├ź»LSIż“4╩¼│õżĘĪóżĮżņżķż“1Ė─ż╬Įj(lu©░)żŁż╩źĘźĻź│ź¾źżź¾ź┐ź▌Ī╝źČż╦źšź¦Ī╝ź╣ź└ź”ź¾żŪ┼ļ║▄ż╣żļĪ╩┐▐1Ī╦ĪŻźżź¾ź┐ź▌Ī╝źČżŽ├▒ż╩żļŪ█└■┴žż└ż▒żŪżóżļż¼ĪóĘQFPGAż╬źĘźĻź│ź¾ź└źżż“4┴žŪ█└■żŪ└▄¶öżĘżŲżżżļĪŻźżź¾ź┐ź▌Ī╝źČż╬╬óĀCŖõż╦└▀ż▒żŲżżżļź▐źżź»źĒźąź¾źūż“źūźĻź¾ź╚┤łż╬źąź¾źūż╦└▄¶öżĘż┐ĖÕĪ󟣟џ├źūż“╚’ż╗żŲ┤░└«ż╣żļĪŻ

ż│ż│ż▐żŪĄĮj(lu©░)ż╩FPGAż╦ż╩żļż╚ĪóTbpsż╬źŪĪ╝ź┐źņĪ╝ź╚ż╚żĘżŲ─╠┐«źąź├ź»ź▄Ī╝ź¾żŪź╚źķźšźŻź├ź»ż╬ź▄ź╚źļź═ź├ź»▓“Š├żžż╬Ń~╬üźŪźąźżź╣ż╚ż╩żļĪŻ

┐▐1ĪĪ4ż─ż╬FPGAź└źżż“źĘźĻź│ź¾źżź¾ź┐Ī╝ź▌Ī╝źČæųż╦ĮĖ└čĪóŪ█└■ĖÕĪó╝┬äóż╣żļ

źóźļźŲźķżŽ┴╚ż▀╣■ż▀┴└żżżŪ28LPźūźĒź╗ź╣ŠW(w©Żng)├ō

▐köĄ(sh©┤)ĪóźóźļźŲźķż╬ź┴ź├źūżŽĪó┴╚ż▀╣■ż▀├ō²ŗż“ź┐Ī╝ź▓ź├ź╚ż╚żĘĪóźūźĒź╗ź├źĄż╦ARM Cortex-A9źŪźÕźóźļź│źóż“ĮĖ└čżĘż┐Cyclone Vż╚Arria VźšźĪź▀źĻż“╚»╔ĮżĘżŲżżżļĪŻ└Łē”ż╬╣ŌżżźūźĒź╗ź├źĄź│źóż“┼ļ║▄żĘż┐ŗ╩¼ż╚ĪóźŽĪ╝ź╔ź”ź©źóż“źūźĒź░źķźÓżŪ┴╚ż▀╬®żŲżļŗ╩¼ż╬╬ŠöĄ(sh©┤)ż“ĮĖ└čż╣żļż│ż╚ż¼▓─ē”ż╦ż╩żĻĪó─Ńź│ź╣ź╚żŪĖ▄Ąę╗┼══ż╬ź½ź╣ź┐ź▐źżź║ż“į~├▒ż╦żŪżŁżļżĶż”ż╦ż╩żļĪŻż│żņż╦żĶż├żŲźĘź╣źŲźÓź│ź╣ź╚ż“▓╝ż▓żĶż”ż╚żżż”┴└żżż¼żóżļĪŻ

ż│ż╬ARMź│źó┼ļ║▄ż╬FPGAż╬źŪźÕźóźļź│źóŗ╩¼żŪżŽĪó├▒╗@┼┘ż╚Ū▄╗@┼┘ż╬╔ŌŲ░Š«┐¶┼└źūźĒź╗ź├źĄżõĪóECCżŪźßźŌźĻż╬Ų╔ż▀ĮążĘź©źķĪ╝ż“▌ö┘ćż╣żļL2źŁźŃź├źĘźÕĪóNeonźßźŪźŻźóźūźĒź╗ź├źĄĪóECC¤²żŁż╬ź▐źļź┴ź▌Ī╝ź╚źßźŌźĻź│ź¾ź╚źĒĪ╝źķĪóQPSI/NANDźšźķź├źĘźÕ/NORźšźķź├źĘźÕż╬ź│ź¾ź╚źĒĪ╝źķĪóżĮż╬┬ŠUSB2.0żõCANĪóEthernetż╩ż╔ż╬╝■╩šźżź¾ź┐źšź¦Ī╝ź╣ż╩ż╔żŌĮĖ└迥żņżŲżżżļĪŻżĄżķż╦║ŪĮj(lu©░)10Gbpsż╬╣ŌÅ]ź╚źķź¾źĘĪ╝źąĪó├▒╗@┼┘Ī”Ū▄╗@┼┘Ī”3Ū▄╗@┼┘ż╬DSPż╩ż╔żŌĮĖ└čżĘżŲżżżļĪŻź╚źķź¾źĘĪ╝źążŽSERDES┬Õż’żĻż╦żŌż╩żļĪŻż│żņż╦żĶżĻĪóźĘź╣źŲźÓż╬Įj(lu©░)╚Šż“┴╚ż▀╣■ż▀ÅUżŪ╣Į└«ż╣żļż│ż╚ż¼żŪżŁĪó║╣╩╠▓ĮżĘż┐żżövŽ®ż└ż▒FPGAżŪźĒźĖź├ź»ż“┴╚żÓżĶż”ż╦żŪżŁżļĪŻ

źóźļźŲźķżŽ│½╚»┤─ČŁżŌŲ▒╗■ż╦┼D×óżĘĪóARMź┘Ī╝ź╣ż╬źĮźšź╚ź”ź©źó│½╚»ź─Ī╝źļżõFPGAĖ■ż▒ż╬źŽĪ╝ź╔ź”ź©źó│½╚»ź─Ī╝źļQsysźĘź╣źŲźÓ┼²╣ńź─Ī╝źļĪóźĘź▀źÕźņĪ╝źĘźńź¾żŌ├ō┴TżĘżŲżżżļĪŻRTLż╬ĖĪŠ┌ż¼Į¬╬╗żĘż┐╗■┼└żŪĪóźŪźąźżź╣?ji©”)ŖŃ~ż╬źĮźšź╚ź”ź©źóż“│½╚»ż╣żļż│ż╚ż¼żŪżŁĪóźŽĪ╝ź╔Ī”źĮźšź╚ż╬Ų▒╗■│½╚»ż¼▓─ē”ż╦ż╩żļĪŻż│żņż╦żĶż├żŲĪó│½╚»┤³┤ųż“ø]Į╠żŪżŁżļĪŻ

ż│ż╬ARMźūźĒź╗ź├źĄŲŌē┼┴╚╣■ÅUFPGAżŽĪó╬Ńż©żąź½źßźķż½żķż╬▒ŪćĄ┐«ęÄ(gu©®)ż“ĮĶ═²ż╣żļövŽ®żŪżŽARMź┘Ī╝ź╣ż╬źėźŪź¬┐«ęÄ(gu©®)ĮĶ═²ż“╣įżżĪó▒ŪćĄ┐«ęÄ(gu©®)ż½żķź»źļź▐żõ┐═ż╬Ų░żŁż╩ż╔ż“ĖĪĮąĪ”▓“└Žż╣żļżĶż”ż╩╝ŖōQĮĶ═²ż“FPGAż¼£pż▒Ęeż─Īóż╚żżż”żĶż”ż╩źĄĪ╝ź┘źżźķź¾ź╣żžż╬▒■├ōż╩ż╔ż╦Ė■żżżŲżżżļĪŻ