źČźżźĻź¾ź»ź╣ż¼źŽźżź©ź¾ź╔ż╬FPGAĪóVirtex-7HTżŪ28Gbpsż╬┼┴┴„╝┬┘xż╦└«Ė∙

ä▌źČźżźĻź¾ź»ź╣żŽĪ󟎟żź©ź¾ź╔ż╬FPGAżŪżóżļVirtex-7 HTż“╗╚żżĪó28Gbpsż╚żżż”Īó«Ć╣ŌÅ]ż╬źĘźĻźóźļź╚źķź¾źĘĪ╝źąż╬└Łē”ż“╝┬Š┌żĘż┐ĪŻ1ź┴ź├źūżŪż│ż╬żĶż”ż╩╣ŌÅ]ż╬źĘźĻźóźļź╚źķź¾źĘĪ╝źążŽĪóż│żņż½żķż╬źżź¾ź┐Ī╝ź═ź├ź╚ż╬ź╚źķźšźŻź├ź»╗\Įj(lu©░)ż╦×┤▒■żĘż┐Īó100Ī┴400Gbpsż╬źąź├ź»ź▄Ī╝ź¾─╠┐«źĘź╣źŲźÓż“╝┬ĖĮż╣żļż┐żßż╦ØŁ═ūż╚ż╩żļĪŻ

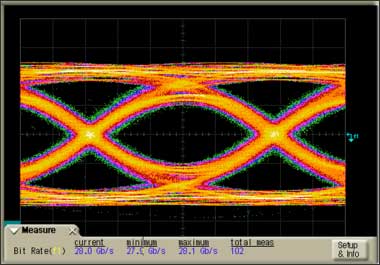

┐▐1ĪĪ28Gbpsź╚źķź¾źĘĪ╝źąż╬źóźżźčź┐Ī╝ź¾

YouTubeż╬│╚ż¼żĻżõźżź¾ź┐Ī╝ź═ź├ź╚źŲźņźėż╬╣Ō▓“ćĄ┼┘▓Įż╩ż╔ĪóźųźĒĪ╝ź╔źąź¾ź╔ż╬▒■├ōż¼╣Łż¼żļż╚Č”ż╦źŪĪ╝ź┐ź╗ź¾ź┐Ī╝żõźąź├ź»ź▄Ī╝ź¾ż╬─╠┐«źĘź╣źŲźÓżŌźčź¾ź»żĘż╩żżżĶż”ż╦┬ė░Ķ╔²ż“╣Łż▓żļØŁ═ūż¼żóżļĪŻżżż┐ż┴ż┤ż├ż│żŪżŽżóżļż¼Īó▒■├ōż╬│╚Įj(lu©░)ó¬╣Ł┬ė░Ķ▓ĮĪóż╬┐╩·tżŽż▐żĄż╦ż╚ż╔ż▐żļż╚ż│żĒż“ē¶żķż╩żżĪŻź═ź├ź╚ź’Ī╝ź»źĘź╣źŲźÓ┤ļČ╚ż╬źĘź╣ź│źĘź╣źŲźÓź║╝ęż╬─┤ØhżŪżŽ2014ŃQż╦żęż╚ĘŅ┼÷ż┐żĻż╬ź╚źķźšźŻź├ź»╬╠ż¼µ£└ż─cżŪ64EBĪ╩ź©ź»źĄźąźżź╚:1EBżŽ10ż╬18ŠĶźąźżź╚Ī╦ż╦żŌ├Żż╣żļĖ½╣■ż▀ż└ż╚żżż”ĪŻ─╠┐«Č╚ŪvżõźŪĪ╝ź┐ź╗ź¾ź┐Ī╝Ī󟻟ķź”ź╔Č╚Ūvż┐ż┴żŽź╚źķźšźŻź├ź»╬╠ż╬╗\Įj(lu©░)ż╦×┤ĮĶż╣żļöĄ(sh©┤)╦Īż“Ė”ē|├µż└ĪŻ2011ŃQāįż«ż╦960Gbpsż╬─╠┐«źĘź╣źŲźÓĪó2014ŃQ░╩æTż╦żŽ1.9Tbpsż╚żżż”╣ŌÅ]ż╬ź▐źļź┴źŲźķźėź├ź╚źĘź╣źŲźÓż¼ĄßżßżķżņżŲżżżļĪŻ

╣ŌÅ]ż╬źŪĪ╝ź┐źņĪ╝ź╚ż¼═ūĄßżĄżņżļ▐köĄ(sh©┤)żŪĪóäóÅøż╬Įj(lu©░)żŁżĄżŽ░▌Ęeż╣żļż│ż╚ż¼ĄßżßżķżņżļĪŻż╣ż╩ż’ż┴Š├õJ┼┼╬üż“▓╝ż▓ż╩ż▒żņżąż╩żķż╩żżĪŻż│ż╬ż┐żßäóÅøŲŌż╬┤łź▄Ī╝ź╔1Ė─ż╬Įj(lu©░)żŁżĄżŽŠ«żĄż»żĘż╩ż¼żķŲ▒żĖŠ├õJ┼┼╬üż“╩▌ż─żĶż”ż╦źŪźąźżź╣ż“żĶżĻ¾Hż»╗╚ż├żŲ└Łē”ż“æųż▓żļż╚żżż”Š}╦Īż“├ōżżżļĪŻ╬Ńż©żą100Gbpsż╬ź▄Ī╝ź╔ż“4ĮŚżŪ400GbpsĪ󵣊├õJ┼┼╬ü60Wż╩żķĪó800Gbpsż╬źĘź╣źŲźÓż“╝┬ĖĮż╣żļż┐żßż╦żŽĪó┤łż╬źįź├ź┴ż“╚ŠžōżĘ60Wż“░▌Ęeż╣żļĪŻ100Gbpsż╬ź▄Ī╝ź╔ż“1ĮŚ╝┬ĖĮż╣żļż┐żßż╦żŽĪó25Gbpsż╬źŪźąźżź╣ż“4ź┴źŃź¾ź═źļĮĖ└čżĘĪóżĮżņż“8ĮŚż╦żĘżŲ400Gbpsż“└▀╝Ŗż╣żļĪŻµ£ŗżŪ32ź┴źŃź¾ź═źļż╚ż╩żļĪŻ100Gbpsż╬źķźżź¾ź½Ī╝ź╔ż“║Ņżļ╬Ńż╚żĘżŲĪó28GbpsżŪ4ź┴źŃź¾ź═źļż╬ź╚źķź¾źĘĪ╝źąż“×óż©ĪóASICż╩ż╔ż╬éb═²▒ķōQĮĶ═²ż“┤▐żÓźķźżź¾ź½Ī╝ź╔ż╦Virtex-7 HTż“╗╚ż”ĪŻ

┐▐2ĪĪCFPĪ╩Centi-formfactor pluggableĪ╦2ż╚Ō}żążņżļźķźżź¾ź½Ī╝ź╔żŪ╝┬ĖĮ

ż┐ż└żĘĪóĖĮ╝┬ż╬övŽ®ż╚żĘżŲĪóźĒźĖź├ź»źŪźąźżź╣ż╚CFP2ź¬źūźŲźŻź├ź»ź╣ż“±Tżųź╚źķź¾źĘĪ╝źążŪżŽźóźżźčź┐Ī╝ź¾ż¼Ø▓╩¼ż╦│½żżżŲżżżļż½Īóż¼ź½ź«ż╦ż╩żļĪŻż│ż╬ż┐żßż╦żŽ░╠┴Ļź╬źżź║żŪżóżļźĖź├ź┐Ī╝ż“żŪżŁżļż└ż▒─Ńż»═▐ż©żļż│ż╚ż¼ĄßżßżķżņżļĪŻ10Gbpsż╬┐«ęÄ(gu©®)┼┴┴„żŪżŽ1źėź├ź╚ż╬╔²żŽ100psż╩ż╬żŪĪó║ŪĮj(lu©░)Ė┬ß×═ŲżŪżŁżļźĖź├ź┐Ī╝żŽ35psż▐żŪż└ż¼Īó28Gbpsż╚ż╩żļż╚╠¾12psż▐żŪż╚ż╩żļĪŻ║Żöv╝┬Š┌żĘż┐┼┴┴„╝┬┘xżŪżŽźķź¾ź└źÓźĖź├ź┐Ī╝ż¼350fsĪóµ£źĖź├ź┐Ī╝żŽ6psż└ż╚żĘżŲżżżļĪŻżĘż½żŌ║ŻövżŽźŲź╣ź╚ź┴ź├źūżŪ╝┬┘xżĘż┐ż┐żßĪó╝┬╬ü├═ż╚ż╩żļż╚żŌż├ż╚▓╝ż▓żķżņżļĪóż╚żżż”ĪŻźėź├ź╚ź©źķĪ╝╬©Ī╩BERĪ╦ż╬╝┬╬üżŽ10ż╬-15ŠĶ░╩▓╝ż└ż╚żżż”ĪŻįużķżņż┐└Łē”╗■żŪż╬Š├õJ┼┼╬üżŽ£½żķż½ż╦żĘż╩żżĪŻ

źĖź├ź┐Ī╝ż“▓╝ż▓żļż┐żßĪóźČźżźĻź¾ź»ź╣żŽźŪźĖź┐źļPLLż“║╬├ōż╗ż║Īóź╬źżź║ż╬Š»ż╩żżLCź┐ź¾ź»╚»┐Čż╬źóź╩źĒź░PLLż“├ōżżż┐ĪŻ▓├ż©żŲĪóča┼┘╩č▓Įż╩ż╔ż╦×┤ż╣żļ┐«ęÄ(gu©®)ż╬╩č▓Įż“─┤┼Dż╣żļż┐żßż╬śOŲ░źŁźŃźĻźųźņĪ╝źĘźńź¾ĄĪē”övŽ®ż“└▀ż▒ż┐ĪŻż│żņżŽ£p┐«ŖõżŪźūźĻź¾ź╚┤łż╬ØŖ└Łż“ź└źżź╩ź▀ź├ź»ż╦żĘż½żŌźóź└źūźŲźŻźųż╦─┤┼Dż╣żļĄĪē”ż└ż╚żĘżŲżżżļĪŻżĄżķż╦źóź╩źĒź░ż╚źŪźĖź┐źļż╬övŽ®ż“╩¼▀`ż╣żļźąźĻźõż“└▀ż▒Īóź╬źżź║ż“5Ī┴15dBžōżķżĘż┐ĪŻźóźżźčź┐Ī╝ź¾ż“░▌Ęeż╣żļż┐żßż╬┴„┐«Ŗõż╬źūźĻź©ź¾źšźĪźĘź╣övŽ®Īó£p┐«Ŗõż╬źżź│źķźżź║övŽ®ż“└▀ż▒żŲżżżļż│ż╚żŽĖ└ż”ż▐żŪżŌż╩żżĪŻ┴„£p┐«ż╣żļ┐«ęÄ(gu©®)żŽ║╣Ų░övŽ®żŪŲ░ż½żĘżŲżżżļĪŻ

╔Į1ĪĪVirtex-7 HTż╬╝ńż╩╗┼══

ż│ż╬FPGAż╦├ōżżż┐źūźĒź╗ź╣żŽ║Ū└Ķ├╝ż╬28nmźūźĒź╗ź╣ĪŻźūźĒź░źķźÓż╣żļż┐żßż╬źĮźšź╚ź”ź©źóżŽż╣żŪż╦Ų■Š}▓─ē”żŪĪóźŪźąźżź╣ż╬Įą▓┘żŽ2012ŃQØi╚Šż“═Į─ĻżĘżŲżżżļĪŻ