ĖČ╗ęöĪŲ░ź╣źżź├ź┴ż“ŠW├ōż╣żļ┐ĘFPGAż“NECż¼źĄź¾źūźļĮą▓┘żž

NECżŽĪóČŌō’ĖČ╗ęöĪŲ░Ę┐ź╣źżź├ź┴ĪųNanoBridgeĪūż“ŠW├ōżĘż┐FPGAż“Īó2017ŃQ3ĘŅż╦ŠÅČ╚Č\Įč┴Ē╣ńĖ”ē|ĮĻż╚Č”Ų▒żŪ│½╚»żĘż┐ż╚╚»╔ĮżĘżŲżżż┐ż¼Īóż│ż╬FPGAż╬źĄź¾źūźļ×æļ]ż“╗ŽżßĪó2017ŃQ┼┘├µż╦źĄź¾źūźļż“Įą▓┘ż╣żļż╚10ĘŅ19Ų³ż╦╚»╔ĮżĘż┐ĪŻĄūĪ╣ż╦źßźŌźĻ░╩│░ż╬▌xŠņżŪĪóŲ³╦▄ż½żķż╬┐ʿʿż╚ŠŲ│öüICż¼┼ąŠņż╣żļĪŻ

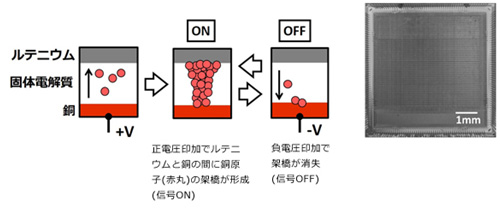

┐▐1ĪĪČŌō’ĖČ╗ęöĪŲ░Ę┐ź╣źżź├ź┴ż╬Ų░║ŅĖČ═²ĪĪĮąųZĪ¦NECĪóŠÅČ╚Č\Įč┴Ē╣ńĖ”ē|ĮĻ

NECż╬ČŌō’ĖČ╗ęöĪŲ░Ę┐ź╣źżź├ź┴NanoBridgeżŽĪóŲ╝┼┼Č╦ż╚╔wöü┼┼▓“䮿“Č┤ż¾żŪRu┼┼Č╦ż╬┤ųż╦┼┼░Ąż“ż½ż▒żļż╚Ų╝ĖČ╗ęż¼Ru┼┼Č╦Ŗõż╦öĪŲ░żĘżŲ┼┼Č╦Ų▒╗╬ż¼ż─ż╩ż¼żĻ┼┼╬«ż¼╬«żņżļĪ╩┐▐1Ī╦ż╚żżż”żŌż╬ĪŻĄš┼┼░Ąż“ż½ż▒żļż╚ĪóŲ╝ż¼ĖĄż╬┼┼Č╦Ŗõż╦╠ßżĻĪó┼┼╬«żŽ╬«żņż╩ż»ż╩żļĪŻż│żņż╦żĶż├żŲĪ󟬟¾ż╚ź¬źšż“╔ĮĖĮż╣żļĪŻż│ż╬ź╣źżź├ź┴ż“╗╚ż├żŲFPGAż“źūźĒź░źķźÓż╣żļĪŻż│ż╬öĄ╝░ż╬ź╗źļżŽĪó╚ŠŲ│öüźŪźąźżź╣ż╬Š╩┼┼╬ü▓Įż“ų`╗žżĘż┐Č”Ų▒Ė”ē|┴╚“ELEAPĪ╩«Ć─Ń┼┼░ĄźŪźąźżź╣Č\ĮčĖ”ē|┴╚╣ńĪ╦żŪżŌĖ”ē|żĄżņżŲżżż┐(╗▓╣═½@╬┴1)ĪŻŠ”├ō▓Įż╣żļż╬żŽż│żņż¼ĮķżßżŲĪŻ

“£═Ķż╬FPGAżŽĪóSRAMż“ź┘Ī╝ź╣ż╦żĘżŲż¬żĻĪóövŽ®ż“└┌żĻü÷ż©żļż┐żßż╬ź╣źżź├ź┴ż╬ĀC└čż¼6ź╚źķź¾źĖź╣ź┐╩¼żóżļż┐żßĀC└čż¼ĮjżŁż½ż├ż┐ĪŻż│ż╬ĖČ╗ęź╣źżź├ź┴ż“ŠW├ōż╣żļż╚ź╣źżź├ź┴ż╬ĀC└迎SRAMź┘Ī╝ź╣ż╬1/30ż╚Š«żĄż»ż╩żĻĪóżĘż½żŌLUTĪ╩źļź├ź»źóź├źūźŲĪ╝źųźļĪ╦ż╚żĘżŲ├ō┴Tż╣żļCMOSź╚źķź¾źĖź╣ź┐żĶżĻæųż╬Ū█└■┴žż╦Ę┴└«ż╣żļż┐żßĪó╝┬ä®┼¬ż╦żŽĀC└čź╝źĒż╚Ė└ż©żļĪŻ

▓├ż©żŲĪóĖČ╗ęöĪŲ░Ę┐ź╣źżź├ź┴ż╬FPGAżŽĪóSRAMż“╗╚ż’ż║Īó▐k┼┘Į±żŁ╣■żÓż╚ź╣źżź├ź┴ėX▌åż¼╩čż’żķż╩żż╔įĦ╚»└Łż╩ż╬żŪźĮźšź╚ź©źķĪ╝ż╦äėżżĪŻż│ż╬ż┐żßĪó▒¦├Ķ└■żõ╩³╝o└■ż╬¾HżżĪóÆņȧĄĪŲŌżõ▒¦├Ķ┤─ČŁżŪż╬┐«═Ļ└Łż¼╣ŌżżĪŻżĘż½żŌ╔įĦ╚»└ŁżŪżóżļż┐żßŠ├õJ┼┼╬üż¼─ŃżżĪŻ

FPGAżŽ└ņ├ōövŽ®ż“źūźĒź░źķźÓżŪ└▀╝ŖżŪżŁżļźĒźĖź├ź»ICż└ż▒ż╦ĪóźĮźšź╚ź”ź©źóź┘Ī╝ź╣ż╬CPUżŪżŽįużķżņż╩żż╣ŌÅ]▓Įż¼▓─ē”żŪżóżļĪŻCPUżŽ║ŪżŌźšźņźŁźĘźųźļż╩ICżŪĪóźĮźšź╚ź”ź©źóż└ż▒żŪśOĮyż╦╣źżŁż╩ĄĪē”ż“╝┬ĖĮżŪżŁżļż¼ĪóźĮźšź╚ź”ź©źóźūźĒź░źķźÓż╦żĶż├żŲżŽźĄźųźļĪ╝ź┴ź¾ż“ż░żļż░żļövżĻĪó▒ķōQÅ]┼┘ż¼ęÆż»ż╩żļż╚żżż”’L┼└ż¼żóżļĪŻż│ż╬ż┐żßĪóHPCĪ╩╣Ō└Łē”ź│ź¾źįźÕĪ╝źŲźŻź¾ź░Ī╦▒■├ōżŪżŽĪó╩┬š`▒ķōQż¼įu┴Tż╩GPUż╚±éż╗żŲ├ōżżżķżņżŲżŁż┐ĪŻHPCż╬├µżŪżŌĪó─╠┐«źŌźŪźÓżŪż╬źąź┐źšźķźż▒ķōQż╬żĶż”ż╦źóźļź┤źĻź║źÓż¼╔w─ĻżĘżŲżżżļżĶż”ż╩övŽ®żŪżŽĪóFPGAżŪ╝┬ĖĮż╣żļż╚żĄżķż╦╣ŌÅ]ż╦ż╩żļĪŻż│ż╬ż┐żßĪóIntelżŽFPGAźßĪ╝ź½Ī╝ż╬Alteraż“āA╝²żĘĪóXilinxżŽQualcommż╚─¾Ę╚żĘż┐ĪŻ

║ŻövĪóNECż¼źĄź¾źūźļĮą▓┘ż╣żļż╬żŽĪó10╦³ź▓Ī╝ź╚Ąķż╬æä╠Žż╬Š«żĄż╩FPGAżŪżóżļż¼Īó║ŻĖÕż╬▌xŠņż“Ė½ż╩ż¼żķIoTĄĪ▀_ż╬╣Ō┼┘▓Įż“ų`╗žż╣ż╚żĘżŲżżżļĪŻIoTźŪźąźżź╣żŽŠ»╬╠¾Hēä¹|ż╬└ż─cż╦ż╩żļż└ż▒ż╦Īóź©ź├źĖź│ź¾źįźÕĪ╝źŲźŻź¾ź░żõź╗ź¾źĄźšźÕĪ╝źĖźńź¾ż╩ż╔ż╬övŽ®żŪFPGAżŽŃ~Ė·ż╩ICż╚ż╩żĻż”żļĪŻ×æļ]żŽ300mmź”ź¦Ī╝źŽż╬źšźĪź”ź¾ź╔źĻż╦░══Ļż╣żļż’ż▒ż└ż½żķĪóNECżŽźšźĪźųźņź╣╚ŠŲ│öüźßĪ╝ź½Ī╝ż╚żżż©żļż¼Īó║Żż╬ż╚ż│żĒźšźĪźųźņź╣źßĪ╝ź½Ī╝ż╦ż╩żļż─żŌżĻżŽż╩ż»ĪóIPż╚żĘżŲźķź¾ź╗ź¾ź╣źėźĖź═ź╣ż“·t│½ż╣żļżĶż”ż└ĪŻ

Ų³╦▄żŪż╬┐ʿʿż╚ŠŲ│öüźėźĖź═ź╣ż╚żĘżŲĪóżŌż”▐kż─Šę▓żĘżĶż”ĪŻ┼ņ»Bź©źņź»ź╚źĒź¾żŽĪóä▌╣±ź┘ź¾ź┴źŃĪ╝ż╬STT (Spin Transfer Technologies)╝ęż╚─¾Ę╚ĪóST-MRAMż╬Š”├ō▓Įż“śŪ┐╩ż╣żļĪóż╚16Ų³╚»╔ĮżĘż┐ĪŻTELż╬MRAMĖ■ż▒ż╬PVDäóÅøż“╗╚żżĪóMRAMż“│½╚»ż╣żļĪŻSTT╝ęż╬MRAMżŌź╣źįź¾ÅRŲ■Ę┐ż╬Äņ─Š╝¦Ążź╚ź¾ź═źļ└▄╣ńĪ╩pMTJĪ╦ż“ŠW├ōż╣żļĪŻST-MRAMżŽźšźķź├źĘźÕżĶżĻżŌ╣ŌÅ]ż╬╔įĦ╚»└ŁźßźŌźĻżŪżóżĻĪóSRAMż╚╚µż┘ź╗źļĀC└čż¼ż║ż├ż╚Š«żĄż»ĪóżĘż½żŌŠ├õJ┼┼╬üżŌŠ«żĄżżĪŻż┐ż└żĘĪóĮ±żŁü÷ż©Öæ╠┐ż¼DRAMżõSRAMżĶżĻżŌż║ż├ż╚Š»ż╩żżż┐żßĪóDRAMż╚źšźķź├źĘźÕż“ż─ż╩ż░ź╣ź╚źņĪ╝źĖź»źķź╣źßźŌźĻż╚żĘżŲż╬┤³┬įż¼ĮjżŁżżĪŻ

STT╝ęż╬pMTJżŽ20nmĘ┬ż▐żŪ╚∙║┘▓Įż¼▓─ē”ż└ż╚Ų▒╝ęż╬ź█Ī╝źÓź┌Ī╝źĖż╦Į±ż½żņżŲż¬żĻĪóTELż╬źūźņź╣źĻźĻĪ╝ź╣żŽĪó└Ķ├╝źĒźĖź├ź»żžż╬ŠW├ōż¼Ń~╦Š£åżĄżņżļĪóż╚Įęż┘żŲżżżļĪŻ└Ķ├╝źĒźĖź├ź»ż╚żŽĪóFPGAż╬ż│ż╚ż╩ż╬ż½ĪóźóźūźĻź▒Ī╝źĘźńź¾źūźĒź╗ź├źĄż╬ż│ż╚ż╩ż╬ż½Ī󿎿├żŁżĻżĘżŲżżż╩żżż¼ĪóźūźĒź╗ź├źĄż╦żŽĮj╬╠ż╬SRAMż¼źņźĖź╣ź┐żõźŁźŃź├źĘźÕż╚żĘżŲĮĖ└迥żņżŲżżżļż┐żßĪóżĮżņżķż╬ÅøżŁ┤╣ż©ż╬▓─ē”└Łż¼żóżļĪŻ

╗▓╣═½@╬┴

1. LEAPĪóFPGA├ōź╣źżź├ź┴ĪóSTT-MRAMĪóTRAMż“VLSI SympożŪ╚»╔Į (2014/6/10)