ź╗ź▀ź│ź¾źĖźŃźčź¾2023Īó└Ķ├╝źčź├ź▒Ī╝źĖź¾ź░Č\Įčż¼¶öĮąĪ╩1Ī╦

ź╗ź▀ź│ź¾źĖźŃźčź¾2023żŪżŽĪóOSATż╬źóź¬źż┼┼╗ęĪóØi╣®µćż╬×æļ]äóÅøż╬TELĪ󟔟ʟ¬ż╚AMATż╬─¾Ę╚Īó╬╔ēäź┴ź├źūż“└č┴žżĘż┐ĖÕż╬źŲź╣ź╚ż“├Ążļźóź╔źąź¾źŲź╣ź╚ż╩ż╔Īó2.5Dżõ3Dż╬ICżõź┴ź├źūźņź├ź╚ż“╝┬äóż╣żļ└Ķ├╝źčź├ź▒Ī╝źĖź¾ź░Č\Įčż¼¶öĮążĘż┐ĪŻ2.5D/3D-ICżõź┴ź├źūźņź├ź╚ż╩ż╔ż“¾H├ōżĘżŲĮĖ└č┼┘ż“ĘQ├╩ż╦æųż▓żļż│ż╚ż¼żŪżŁżļĪŻ└Ķ├╝źčź├ź▒Ī╝źĖź¾ź░ż╬äóÅøźßĪ╝ź½Ī╝ż¼¶öĮążĘż┐ĪŻ1ŗż╚2ŗż╦╩¼ż▒żŲĘŪ║▄ż╣żļĪŻ

┐▐1ĪĪĄūżĘżųżĻż╦ź╗ź▀ź│ź¾źĖźŃźčź¾żŽÜŌż’ż├ż┐ĪĪ┼ņ»Bźėź├ź░źĄźżź╚ż╬┼ņ1Ī┴6ź█Ī╝źļµ£ŗż╚┐ʿʿż┼ņŻĘż╚┼ņ8ź█Ī╝źļż“žéżßż┐

12ĘŅ13Ų³Ī┴15Ų³Īó┼ņ»Bźėź├ź░źĄźżź╚żŪ│½╠¢żĄżņż┐ź╗ź▀ź│ź¾źĖźŃźčź¾2023Ī╩┐▐1Ī╦żŽĪóź│źĒź╩░╩ØiżĶżĻżŌÜŌż’ż├ż┐ĪŻ╚ŠŲ│öüŠÅČ╚ż╬─_═ū└Łż¼Ė½─ŠżĄżņĪó│žÖ┌żõ╣{żżųö└Łż¼╚ŠŲ│öü×æļ]äóÅøż╬źųĪ╝ź╣żŪ┐╚ż“ŠĶżĻĮążĘżŲÅBż“╩╣ż»ųeż¼żóż┴żķż│ż┴żķżŪĖ½£pż▒żķżņż┐ĪŻ2022ŃQż╦5╦³1480ć@ż└ż├ż┐═ĶŠņŪvżŽĪó║ŻŃQżŽ8╦³5282ć@ż╚─Ęż═æųż¼ż├ż┐ĪŻźųĪ╝ź╣żŽ┼ņ»Bźėź├ź░źĄźżź╚ż╬┼ņ1Ī┴6ź█Ī╝źļż▐żŪż╬µ£┤█ż╚┐ʿʿżź█Ī╝źļ7ż╚8ż“žéżßż┐ĪŻ

ź╗ź▀ź│ź¾źĖźŃźčź¾2023żŪżŽ└Ķ├╝źčź├ź▒Ī╝źĖź¾ź░Č\Įčż¼ÅRų`żĄżņż┐ĪŻ┼ņ»B╣®Č╚Įj│žØŖŪżČĄĶbż╬ʬ┼─═╬▐k╬rĢ■żŽĪóź┴ź├źūźņź├ź╚żõź┴ź├źūĪ╩ź└źżĪ╦ż╚ż╬┤ųż“źĘźĻź│ź¾źżź¾ź┐Ī╝ź▌Ī╝źČżŪżŽż╩ż»ĪóżŌż├ż╚Š«żĄż╩źųźĻź├źĖź┴ź├źūżŪ└▄¶öż╣żļČ\Įčż“źóź¬źż┼┼╗ęż╬źųĪ╝ź╣żŪĖ½ż╗żŲżżż┐ĪŻż│żņżŽĪó║ŲŪ█└■┴žż“Ę┴└«żĘżŲżżżļźųźĻź├źĖź┴ź├źūż╚Īóź┴ź├źūźņź├ź╚żõź┴ź├źūż“CuĪ╩Ų╝Ī╦ż╬ź▐źżź»źĒźįźķĪ╝żŪ└▄¶öżĘżĶż”ż╚żżż”żŌż╬Ī╩┐▐2Ī╦ĪŻIntelż╬EMIBĪ╩Embedded Multi-die Interconnect BridgeĪ╦Č\Įčż╚ō¶żŲżżżļż¼ĪóEMIBżŪżŽźųźĻź├źĖź┴ź├źūż“źūźĻź¾ź╚övŽ®┤łż╦ļmżß╣■ż¾żŪż¬ż»ØŁ═ūż¼żóżļĪŻż│żņż╦×┤żĘżŲĪóʬ┼─ČĄĶbż╬öĄ╦ĪżŽĪóź┴ź├źūźņź├ź╚żõź┴ź├źū┤ųż“źųźĻź├źĖź┴ź├źūżŪ└Ķż╦ź▐źżź»źĒCuźįźķĪ╝ż“├ōżżżŲ└▄¶öżĘĪóżĮż╬ĖÕżŪź┴ź├źūźņź├ź╚żõź┴ź├źūżŽ┤łż╚└▄¶öż╣żļĪŻEMIBżĶżĻżŌį~├▒ż╩╣®µćż╦ż╩żļĪŻ

![“£═Ķż╬╚ŠŲ│öüĮĖ└čövŽ®ż╚ź┴ź├źūźņź├ź╚ĮĖ└č╣Įļ]╚µ│ė / ┼ņ»B╣®Č╚Įj│ž](/archive/editorial/industry/img/20231226-TIT.png)

┐▐2ĪĪ┼ņ»B╣®Č╚Įj│žż╬ʬ┼─═╬▐k╬rČĄĶbż¼│½╚»żĘż┐źčź├ź▒Ī╝źĖź¾ź░Č\ĮčĪĪĮąųZĪ¦┼ņ»B╣®Č╚Įj│ž

└Ķ├╝źčź├ź▒Ī╝źĖżŽŪ█└■╔²ż¼ĖĮ║▀║Ū└Ķ├╝ż╬50µmµć┼┘ż½żķ10µm░╩▓╝ż╬▓├╣®ż¼ĄßżßżķżņżļĪŻĘ¬┼─ČĄĶbż╬ź▐źżź»źĒźįźķĪ╝żõźųźĻź├źĖź┴ź├źūŲŌż╬║ŲŪ█└■┴žż╬Ę┴└«ż╩ż╔ż╦żŽż│żņż▐żŪż╬Ū█└■╔²ż╚żŽĘÕż¼░Ńż”╚∙║┘▓├╣®Č\Įčż¼ØŁ═ūż╦ż╩żļĪŻ

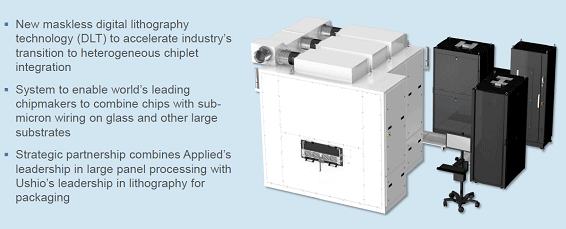

Applied Materialsż╚ź”źĘź¬ż¼─¾Ę╚żĘżŲŠ»╬╠¾Hēä¹|├ōż╬źĻźĮź░źķźšźŻäóÅøż“│½╚»żĘżŲżżżļĪŻźŪźĖź┐źļźĻźĮź░źķźšźŻż╚Ō}żųżĮż╬äóÅøżŽĪóź▐ź╣ź»źņź╣żŪŪ█└■źčź┐Ī╝ź¾ż“źżź¾ź┐Ī╝ź▌Ī╝źČżõź¼źķź╣ż╩ż╔ż╬övŽ®┤łĪ╩źĄźųź╣ź╚źņĪ╝ź╚Ī╦ż╦─Š└▄ķWż»ĪŻż│ż╬źĻźĮź░źķźšźŻČ\ĮčżŪżŽŪ█└■╔²2µm░╩▓╝ż╬Ū█└■źčź┐Ī╝ź¾ż╦×┤▒■żŪżŁżļĪŻż│żņż▐żŪż╬źūźĻź¾ź╚övŽ®┤łĖ■ż▒ż╬źĻźĮź░źķźšźŻżŽ10µm░╩æųż╬Ū█└■źčź┐Ī╝ź¾ż└ż├ż┐ż┐żßĪó╚ŠŲ│öüź”ź¦Ī╝źŽĖ■ż▒ż╬źĄźųź▀ź»źĒź¾ż╬źĻźĮź░źķźšźŻäóÅøżŪżŽ×┤▒■żŪżŁż╩ż½ż├ż┐ĪŻźūźĻź¾ź╚övŽ®ż╚źĘźĻź│ź¾ź”ź¦Ī╝źŽż╚ż╬┤ųż“ļmżßżļźĻźĮź░źķźšźŻäóÅøż¼║Żövż╬DLTĪ╩Digital Lithography TechnologyĪ╦äóÅøżŪżóżļĪŻ

┐▐3ĪĪApplied Materialsż╚ź”źĘź¬ż¼Č”Ų▒│½╚»żĘż┐DLTźĻźĮź░źķźšźŻäóÅøĪĪĮąųZĪ¦Applied Materials

ż╩ż╝ż│ż╬äóÅø│½╚»ż¼ØŁ═ūż└ż├ż┐ż½ĪŻ═ūĄßż¼äėżżż╬żŽÖ┌└«AIżŪżóżļĪŻĄĮjż╩źĮźšź╚ź”ź©źóż╬Ö┌└«AIż“│žØ{żĄż╗żļż╬ż╦─╣żż╗■┤ųż¼ż½ż½ż├żŲżżż┐ĪŻź┴źŃź├ź╚GPTż╬│žØ{ż╦żŽ300Ų³żŌż½ż½ż├ż┐ż╚Ė└ż’żņżŲżżżļĪŻż│ż╬ż┐żßĮj╚Šż╬AIźĮźšź╚ź”ź©źóČ\ĮčŪvżŽź│Ī╝ź╔ż¼─╣ż╣ż«żļż┐żßĪóźĮźšź╚│½╚»ż“ż█ż▄żóżŁżķżßżŲżżż┐ĪŻ│žØ{ż╦ØŁ═ūż╩GPUż╬└Łē”ż¼╔į’BżĘżŲżżż┐ż½żķż└ĪŻĄĮjż╩źĮźšź╚ż╦żŽĄĮjż╩╚ŠŲ│öüź┴ź├źūżŪ×┤Ń^ż╣żļżĘż½ż╩żżĪŻżĘż½żĘĪóźņź┴ź»źļźĄźżź║żŪź┴ź├źūźĄźżź║żŽ»éż▐ż├żŲżĘż▐ż”ĪŻżĘż½żŌĮjżŁż╩źĄźżź║ż╬ź┴ź├źūżŽ╩Ōé╬ż▐żĻż¼═Ņż┴żŲżĘż▐ż”ĪŻ

żĮż│żŪź┴ź├źūŲŌż╬Š«żĄż╩ĮĖ└čövŽ®żõIPż“ź┴ź├źūźņź├ź╚ż╚żżż”Ę┴żŪ└┌żĻĮążĘżŲĪ󿥿▐żČż▐ż╩źūźĒź╗ź├źĄż╬ź┴ź├źūĪ╩ź└źżż╚żŌżżż”Ī╦ż“╩┐ĀCż╦┼ļ║▄żĘż┐żĻ3╝ĪĖĄ┼¬ż╦─_ż═ż┐żĻżĘżŲźžźŲźĒĮĖ└čövŽ®ż“╣Į└«ż╣żļĪó└Ķ├╝źčź├ź▒Ī╝źĖČ\Įčż¼┼ąŠņżĘż┐ĪŻż│ż╬┤łĪ╩źĄźųź╣ź╚źņĪ╝ź╚Ī╦ż╦┐¶µm╔²ż╬Ū█└■ż“ķWż»ż╬ż¼Appliedż╚ź”źĘź¬ż¼│½╚»żĘż┐DLTżŪżóżļĪŻź┴ź├źūźĄźżź║ż╚żŽ╠Ą┤žĘĖż╩ĮĖ└čövŽ®ż“║Ņżņżļż┐żßĪóÖ┌└«AIż╬żĶż”ż╩ĮjżŁż╩ź┴ź├źūżŌ│┌ż╦║Ņżļż│ż╚ż¼żŪżŁżļĪŻżĘż½żŌÖ┌└«AIĖ■ż▒ż╬ICż└ż╚ĪóźßźŌźĻżõCPUż█ż╔ż╬Ö┌ŠÅ╬╠żŽØŁ═ūż╩żżż┐żßĪóź▐ź╣ź»źņź╣żŪż╬Ö┌ŠÅż¼▓─ē”ż└ĪŻż▐ż┐Īóź╣źŲź├źčż╚░ŃżżĪóźņź┴ź»źļČŁ─cżŪż╬źčź┐Ī╝ź¾ż╬Ž─ż▀ż¼ż╩żżĪŻ

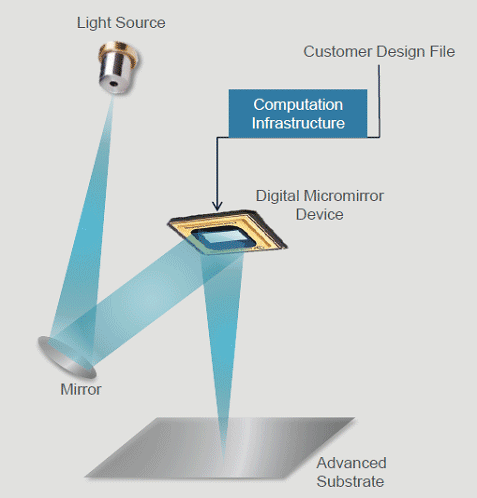

ż╩ż╝źŪźĖź┐źļźĻźĮź░źķźšźŻż╚Ō}żųż╬ż½ĪŻżĮż╬ź½ź«żŽĪóźĻźĮź░źķźšźŻźĘź╣źŲźÓż╦ĪóźŪźĖź┐źļź▀źķĪ╝źŪźąźżź╣Ī╩DMDĪ╦ż“╗╚ż├żŲżżżļż½żķż└Ī╩┐▐4Ī╦ĪŻDMDżŽ48╦³Ī┴800╦³Ė─ż╬MEMSČ\Įčż╬ź▀źķĪ╝Ī╩¬ÜĪ╦ż“ź▐ź╚źĻź»ź╣æųż╦╩┬ż┘ż┐źŪźąźżź╣żŪżóżļĪŻTexas Instrumentsż¼│½╚»żĘż┐Č\ĮčżŪĪó▐k╚╠ż╬▒Ū▓Ķ┤█żŪźūźĒźĖź¦ź»ź┐ż╚żĘżŲ╗╚ż’żņżŲżżżļĪŻövŽ®ż╬Ū█└■źčź┐Ī╝ź¾żŽDMDż“Ņ~Ų░ż╣żļż│ż╚żŪķWż½żņżļĪŻĖ▄Ąęż╬övŽ®└▀╝ŖźšźĪźżźļż“Ų■╬üż╣żļż│ż╚żŪźčź┐Ī╝ź¾ż“ķWż»ĪŻ

┐▐4ĪĪDLTż╬Ų░║ŅĖČ═²żŽDMDźŪźąźżź╣ż“╗╚ż├żŲźčź┐Ī╝ź¾ż“ķWż»ĪĪĮąųZĪ¦Applied Materials

ź”źĘź¬żŽż│żņż▐żŪźūźĻź¾ź╚övŽ®┤łĖ■ż▒ż╬ź╣źŲź├źčż“4000±ś░╩æųĮą▓┘żĘżŲżŁż┐ż╚żżż”╝┬└ėż¼żóżļĪŻżĘż½żĘ║Żövż╬żĶż”ż╩źņĪ╝źČĪ╝─ŠķWäóÅøżŽĮķżßżŲżŪĪóApplied ż╚Č”Ų▒żŪ│½╚»ż╦ż│ż«ż─ż▒ż┐ĪŻApplied żŽż│ż╬Č\Įč│½╚»ż╦└šŪżż“Ęeż┴Ī󟔟ʟ¬żŽźĻźĮź░źķźšźŻäóÅøż“╚╬Ūõż╣żļĪŻż╣żŪż╦╩Ż┐¶ż╬ź½ź╣ź┐ź▐ż╦Įą▓┘żĘżŲäh▓┴ż“£pż▒żŲżżżļż╚├╩│¼ż└ż╚żżż”ĪŻ║Żövż╬×æē俎2µm└■╔²ż“×┤ō■ż╚żĘżŲżżżļż¼Īó╝ĪżŽ1µmż╬źĻźĮź░źķźšźŻźĘź╣źŲźÓ│½╚»ż╚żżż”źĒĪ╝ź╔ź▐ź├źūżŌĘeż├żŲżżżļĪŻ

Ī╩ŗī2ŗżž¶öż»Ī╦