Ų³╦▄ż╬ź╣źčź│ź¾╔┘▀tżŽArmź│źóź┘Ī╝ź╣żŪ└ż─c▐kż╬└Łē”ż“æ═įu

ź╣Ī╝źčĪ╝ź│ź¾źįźÕĪ╝ź┐ż╬└Łē”źķź¾źŁź¾ź░ż╚żĘżŲ6ĘŅżŪż╬TOP500ż¼╚»╔ĮżĄżņĪóŲ³╦▄ż╬ź╣źčź│ź¾Īų╔┘▀tĪūż¼ź╚ź├źūż“æ═įuĪó415PFLOPSż╬LINPACK└Łē”ż“┐āżĘż┐ĪŻCPUżĮż╬żŌż╬żŽ╔┘╗╬─╠ż╬└▀╝Ŗż└ż¼ĪóCPUź│źóż╦żŽArmv8.2-A SVEĪ╩Scalable Vector ExtensionĪ╦źóĪ╝źŁźŲź»ź┴źŃż¼╗╚ż’żņżŲżżżļĪŻArmż╬╠┐╬ßź╗ź├ź╚ż“╗╚żżĪóźßźŌźĻż“CPUż╦▓─ē”ż╩Ė┬żĻŖZż┼ż▒żļż╚Č”ż╦ĪóCPUŲ▒╗╬ż╬ź═ź├ź╚ź’Ī╝ź»ż╦żŽ╔┘╗╬─╠ż¼│½╚»żĘż┐ĪųTofuźżź¾ź┐Ī╝ź│ź═ź»ź╚DĪūż“║╬├ōżĘż┐ĪŻ

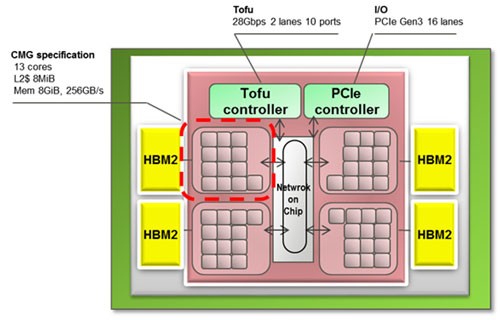

┐▐1ĪĪCPU1Ė─ż╬ŲŌŗ╣Į└«ĪĪĮąųZĪ¦╔┘╗╬─╠

Ų³╦▄ż╬ź╣źčź│ź¾ż¼ź╚ź├źūż╦ż╩ż├ż┐ż╬żŽ8ŃQ╚ŠżųżĻĪŻ┼÷╗■ż╬Īų»BĪūżŪżŽ╔┘╗╬─╠ż╬CPUźóĪ╝źŁźŲź»ź┴źŃSPARC64ż“╗╚ż├ż┐ż¼Īó║ŻövżŽArmż╬64źėź├ź╚CPUź│źóż“52Ė─Īó1ź┴ź├źūż╦ĮĖ└čżĘżŲżżżļĪŻź┴ź├źūµ£öüż“4ż─ż╬źųźĒź├ź»ż╦╩¼ż▒Īó1źųźĒź├ź»ŲŌż╦▒ķōQź│źóż“12Ė─ĪóöUĖµ├ōźóźĘź╣ź┐ź¾ź╚ź│źóż“1Ė─ż╚L1/L2źŁźŃź├źĘźÕż“ĮĖ└čżĘżŲżżżļĪŻ

CPUź│źóż╚źßźŌźĻż“żŪżŁżļż└ż▒ŖZż┼ż▒żļż│ż╚żŪź┴ź├źūŲŌż╬╝ŖōQÅ]┼┘ż“æųż▓ĪóźųźĒź├ź»┤ųż“NICĪ╩Network in ChipĪ╦ź╣źżź├ź┴żŪ└▄¶öż╣żļż│ż╚żŪźųźĒź├ź»┤ųż╬ęÆūāż“ø]Į╠żĘż┐ĪŻĘQźųźĒź├ź»żŽĮj═Ų╬╠źßźŌźĻHBM2żŪ└▄¶öżĘĪóĮj╬╠ż╬źŪĪ╝ź┐ż“1024 GB/sż╚żżż”«Ć╣ŌÅ]żŪźóź»ź╗ź╣ż╣żļĪŻ

żĄżķż╦ż│ż╬1źčź├ź▒Ī╝źĖż╬CPUż“1ø▄öüż╦384Ė─┼ļ║▄żĘĪóCPUŲ▒╗╬ż“Tofuźżź¾ź┐Ī╝ź│ź═ź»ź╚żŪ└▄¶öż╣żļĪŻ╔┘▀tż╬źĘź╣źŲźÓżŽ396±śż╬ø▄öüż║żķżĻż╚╩┬ż┘ż┐żŌż╬Ī╩┐▐2Ī╦ż╚ż╩ż├żŲżżżļĪŻ

┐▐2ĪĪ║Żövż╬╔┘▀tżŪżŽź╣źčź│ź¾ż╬ø▄öüż“396±śŲ░║ŅżĄż╗ż┐ĪĪĮąųZĪ¦═²▓Į│žĖ”ē|ĮĻĪó╔┘╗╬─╠

CPU1Ė─żŽĪóTSMCż╬7nm FinFETźūźĒź╗ź╣żŪ×æļ]żĘĪó87▓»8600╦³ź╚źķź¾źĖź╣ź┐ż¼ĮĖ└迥żņżŲżżżļĪŻźčź├ź▒Ī╝źĖżĄżņż┐ICż╬┐«ęÄźįź¾żŽ594źįź¾ĪŻ

Armż╬SVEżŽĪóź┘ź»ź╚źļ▒ķōQ▓─ē”żŪĪó║ŪĮj512źėź├ź╚╔²ż╬SIMDĪ╩Single Instruction Multiple DataĪ╦źŪĪ╝ź┐żŪ▒ķōQż╣żļĪŻ

ż▐ż┐ĪóĄĪ│Ż│žØ{żõźŪźŻĪ╝źūźķĪ╝ź╦ź¾ź░ż╬│žØ{żŌ┐õébżŌ▓─ē”ż╩żĶż”ż╦Īó16źėź├ź╚╔ŌŲ░Š«┐¶┼└▒ķōQFP16żõ8źėź├ź╚┼D┐¶▒ķōQINT8ż╩ż╔ż╬┐õéb▒ķōQżŌ▓─ē”ż╩żĶż”ż╦ĪóźŪĪ╝ź┐╔²ż“╩čż©żķżņżļ╣Į└«ż╦ż╩ż├żŲżżżļĪŻżĮżņżŌ┐õébżŪżŽ╗@┼┘ż“8źėź├ź╚ż╦═Ņż╚żĘĪóŠ├õJ┼┼╬üż╬║’žōż“┐▐ż├żŲżżżļĪŻ

▒ķōQż“║Ū═ź└Ķż╣żļź╣źčź│ź¾żŽĪóż│żņż▐żŪCPUż¼└Łē”ż“»éżßżļż╚żĘżŲSPARCź┴ź├źūż“żŽżĖżßŲ╚śO│½╚»ż“Ų³╦▄żŪżŽ┐õ┐╩żĘżŲżŁż┐ż¼ĪóArmź┘Ī╝ź╣ż╬źóĪ╝źŁźŲź»ź┴źŃżŪżŌ║Ū╣Ō└Łē”ż¼įużķżņżļż│ż╚ż¼ż’ż½ż├ż┐ĪŻArmż╬ISAĪ╩╠┐╬ßź╗ź├ź╚źóĪ╝źŁźŲź»ź┴źŃĪ╦ż“╗╚żżż╩ż¼żķĪóSVEż╚żżż”ź┘ź»ź╚źļ▒ķōQż“│╚─źĪ”╝{▓├ż╣żļż│ż╚żŪĪó▒ķōQż╦ĮĖ├µżŪżŁżļżĶż”ż╦żĘż┐ĪŻ═ūżŽźßźŌźĻż╚CPUż╚ż╬š{▀`ż“żŪżŁżļż└ż▒ø]ż»żĘĪóCPUŲ▒╗╬ż“ż─ż╩ż░Ū█└■ż“├▒ż╩żļźąź╣öĄ╝░żŪżŽż╩ż»Īóź╣źżź├ź┴öĄ╝░żŪ└┌żĻü÷ż©żļż│ż╚żŪ└Łē”ż“æųż▓żķżņżļż│ż╚żŌ║ŪŖZż’ż½ż├żŲżŁżŲżżżļĪŻżĄżķż╦źßźŌźĻźąź╣╔²żŌż│żņż▐żŪżŽź▄ź╚źļź═ź├ź»ż└ż├ż┐ż┐żßĪóż│żņżŌźšźņźŁźĘźųźļż╦│╚─źż╣żļöĄ╦Īżžż╚╩čż’ż├ż┐ĪŻż│ż”żżż├ż┐▐kŽóż╬źŲź»ź╬źĒźĖĪ╝żŽĪóCPU▐k╩š┼▌ż└ż├ż┐ż│żņż▐żŪż╬╣═ż©ż“▓■żßżļ╬╔żżĄĪ▓±ż╦ż╩ż├ż┐ż╚żżż©żĮż”ż└ĪŻ

╗▓╣═½@╬┴

1. Japan Captures TOP500 Crown with Arm-Powered Supercomputer (2020/06/22)