┼ņĮj(lu©░)ż╬AIź┴ź├źū└▀╝ŖĄ“┼└ż¼īÖŲ░│½╗ŽĪóź½ź«żŽźŪźČźżź¾źŽź”ź╣

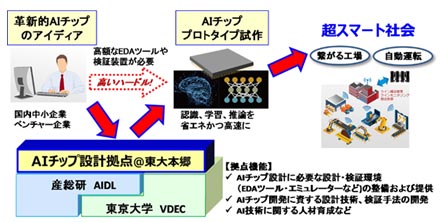

┼ņ»BĮj(lu©░)│žżŽĪóŠÅČ╚Č\Įč┴Ē╣ńĖ”ē|ĮĻż╚Č”Ų▒żŪĪóAIĪ╩┐═╣®ē¶ē”Ī╦ź┴ź├źūż“│½╚»ż╣żļż┐żß└▀╝ŖĄ“┼└ż“╦▄Ā┘źŁźŃź¾źčź╣ŲŌż╦żóżļ╝Ø┼─└Ķ├╝ē¶źėźļż╦├█żŁĪóīÖŲ░ż“│½╗ŽżĘż┐ĪŻ└▀╝Ŗź─Ī╝źļżõźŽĪ╝ź╔ź”ź©źóĖĪŠ┌ż╣żļż┐żßż╬éb═²ź©ź▀źÕźņĪ╝ź┐ż“┬Ęż©Īó├µŠ«ż╬ź┘ź¾ź┴źŃĪ╝┤ļČ╚ż“?y©żn)┤ō?j©┤)ż╦─¾ČĪż╣żļĪŻ

┐▐1ĪĪ┼ņĮj(lu©░)╦▄Ā┘ż╦Ą“┼└ż“╣Įż©ż┐AIź┴ź├źū│½╚»źĄź▌Ī╝ź╚ĪĪĮąųZĪ¦┼ņ»BĮj(lu©░)│ž

║ŻĘŅĪó│½╠¢żĄżņż┐ĪųAIź┴ź├źū└▀╝ŖĄ“┼└īÖŲ░│½╗ŽĄŁŪ░źĘź¾ź▌źĖź”źÓĪūżŪżŽĪóŠÅČ╚Č\Įč┴Ē╣ńĖ”ē|ĮĻż╬├µ╚Ł═²Ą£─╣żõ┼ņĮj(lu©░)╔¹│ž─╣ż╬Š«┤ž╔ę“}Ģ■ż“żŽżĖżßĪó¾Hż»ż╬öĄ(sh©┤)Ī╣ż╬░¦╗óż¼żóżĻĪóĒ×ķL╠OĮj(lu©░)│žż╬╦▄õø┐┐┐═ČĄĶbż¼ĄŁŪ░╣ų▒ķż“╣įż├ż┐ĪŻAIź┴ź├źū│½╚»ż“┐╩żßżŲżŁż┐╦▄õøČĄĶbżŽĪóż│żņż▐żŪż╬CPUż╚żŽ░Ńż”ĪóAIĮĶ═²ż╬ź’Ī╝ź»źĒĪ╝ź╔ż╦┤¾żĻ┼║ż”ź│ź¾źįźÕĪ╝ź┐ż¼ØŁ═ūż╚żĄżņżļż╚żĘżŲĪóAIź┴ź├źūż╬ØŁ═ū└Łż“┴╩ż©ż┐ĪŻ

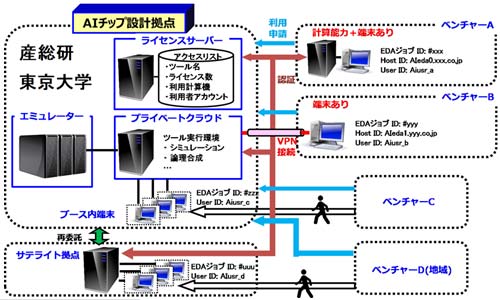

┐▐2ĪĪżżżĒżżżĒż╩AIź┘ź¾ź┴źŃĪ╝ż╦╗╚ż├żŲżŌżķż”╗┼┴╚ż▀ĪĪĮąųZĪ¦┼ņ»BĮj(lu©░)│ž

AIź┴ź├źūżŽĪó╗═ō¦▒ķōQż“├µ┐┤ż╚ż╣żļĪų╝ŖōQĪūż¼įu┴Tż╩“£═Ķż╬ź│ź¾źįźÕĪ╝ź┐ż╚╚µż┘Īó─Š┤Č┼¬Ī”ē¶ē”┼¬ż╩Š╩¾ĮĶ═²ż“įu┴Tż╚ż╣żļĪŻż│ż╬ż┐żßĪóżĮżņżŠżņ▌ö┤░żĘ╣ńż├żŲ├ō²ŗż╦▒■żĖżŲ╗╚ż”ż│ż╚ż¼╦Šż▐żĘżżĪŻ“£═Ķż╬ź│ź¾źįźÕĪ╝ź┐ż¼Š}¶öżŁĘ┐Š╩¾ĮĶ═²ż╚ż╣żņżąĪóAIź│ź¾źįźÕĪ╝źŲźŻź¾ź░żŽźŪĪ╝ź┐źšźĒĪ╝Ę┐ż╚Ė└ż├żŲżĶżżż└żĒż”ĪŻ╦▄õøĢ■żŽĪó┐ʿʿżAIź│ź¾źįźÕĪ╝źŲźŻź¾ź░ż╬źšźņĪ╝źÓź’Ī╝ź»ż““£═Ķż╬Š}¶öżŁĘ┐ź│ź¾źįźÕĪ╝źŲźŻź¾ź░ż╚░ŃżżĪóźĮźšź╚ź”ź©źóż╚źŽĪ╝ź╔ź”ź©źóż¼ż─ż╩ż¼żļ±T£I┼└(ź╬Ī╝ź╔)ż¼¾H┐¶┘T║▀ż╣żļż╚╣═ż©żŲżżżļĪ╩┐▐3Ī╦ĪŻż│ż╬ż┐żßĪó±T£I┼└ż“»éżßż┐żŌż╬ż¼źšźņĪ╝źÓź’Ī╝ź»ż“öU(ku©░)ż╣żļż└żĒż”ż╚═Į„[ż╣żļĪŻ

┐▐3ĪĪ┐ʿʿżźóĪ╝źŁźŲź»ź┴źŃż¼ĄßżßżķżņżŲżżżļĪĪĮąųZĪ¦Ē×ķL╠OĮj(lu©░)│ž ╦▄õø┐┐┐═ČĄĶb

±T£I┼└ż“»éżßżļż┐żßż╦żŽĪ󿥿▐żČż▐ż╩AIź┴ź├źūż“║ŅżĻĪóżĮż╬├µż½żķ└@├ō└Łż“Ė½ż─ż▒żļż│ż╚ż¼ź½ź«ż“É█żļĪŻż└ż½żķĪóAIź┴ź├źūż╬│½╚»ż¼Šåż¼żņżŲżżżļĪŻ╦▄õøĢ■ż¼AIź┴ź├źūż“│½╚»żĘżŲżżżļż╬żŽż│ż╬ż┐żßż└ĪŻä▌╣±żŪżŽDARPAĪ╩╣±╦╔┴ĒŠ╩ż╬╣Ō┼∙Ė”ē|╝Ŗ▓ĶČ╔Ī╦ż¼╝ńŲ│ż╣żļCRAFTźūźĒźĖź¦ź»ź╚żõ±śŽčż╬CICĪ╩Chip Implementation CenterĪ╦ż╩ż╔ż¼AIź┴ź├źū│½╚»ż“źĻĪ╝ź╔żĘżŲż¬żĻĪó├µ╣±żŌ1000▓»▀ģæä╠Žż╬AIź┴ź├źūż╬╣±▓╚źūźĒźĖź¦ź»ź╚ż¼żóżļż╚żżż”ĪŻŲ³╦▄żŪżŌAIź┴ź├źūż╬│½╚»ż“śŪ┐╩ż╣żļĪó║Żövż╬┼ņĮj(lu©░)Ī”ŠÅ┴ĒĖ”Č”Ų▒źūźĒźĖź¦ź»ź╚ż“╝āĘ▐ż╣żļĪŻ

└«Ė∙ż╬ź½ź«żŽźŪźČźżź¾źŽź”ź╣

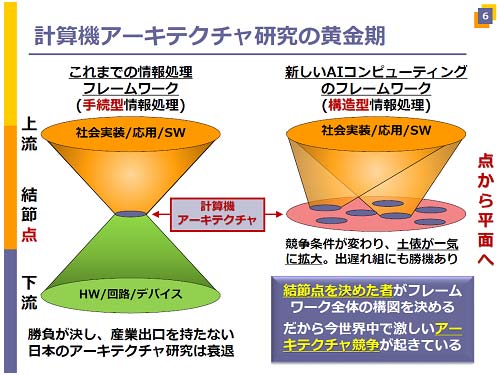

ŠÅ┴ĒĖ”ż¬żĶżė┼ņĮj(lu©░)żŽĪóĘą║čŠÅČ╚Š╩ĪųŠÅČ╚Č\Įč╝┬├ō▓Į│½╚»Ą£Č╚õJ▌öÕ\ČŌĪ╩AIź┴ź├źū│½╚»▓├Å]ż╬ż┐żßż╬ĖĪŠ┌┤─ČŁ┼D×óĄ£Č╚Ī╦ĪūĪ󿬿ĶżėNEDOĪųAI ź┴ź├źū│½╚»▓├Å]ż╬ż┐żßż╬źżź╬ź┘Ī╝źĘźńź¾┐õ┐╩Ą£Č╚Ī┐Ė”ē|│½╚»╣Óų`ŁóĪ¦AI ź┴ź├źū│½╚»ż“▓├Å]ż╣żļČ”─╠┤╚ūČ\Įčż╬│½╚»Īūż╦Č”Ų▒żŪ─¾░ŲżĘĪó║╬┘IżĄżņż┐ż│ż╚żŪŽ×ĮBż½żķż╬Įą½@ż“įużŲżżżļĪŻ

AIź┴ź├źūż“└▀╝Ŗż╣żļźŪźČźżź╩Ī╝Ė■ż▒ż╬ź─Ī╝źļż“┬Ęż©żļż│ż╚żŌ─_═ūż└ż¼ĪóVLSI└▀╝ŖżŪżŽVHDLżõVerilogż╚żżż├ż┐VLSI└▀╝ŖĖ└Ėņż“Ø{įużĘż╩ż▒żņżąż╩żķż╩żżż┐żßĪóAIż╬źóźļź┤źĻź║źÓ│½╚»Ūvż╦ż╚ż├żŲĪóVLSIĖ└ĖņØ{įuż¼ź½ź┘ż╦ż╩żļĪŻAIż╬═źżņż┐źóźļź┤źĻź║źÓ│½╚»ŪvżŽĪóVLSI└▀╝ŖĖ└Ėņż╩ż╔żżż▐żĄżķØ{įużĘż┐ż»ż╩żżĪŻżĮż╬żĶż”ż╩╗■┤ųż¼żóżņżąĪóżŌż├ż╚╬╔żżźóźļź┤źĻź║źÓ│½╚»ż╦ĮĖ├µżĘż┐żżĪŻż│ż╬╠õ¼öż“▓“»éżĘżŲż»żņżļż╬ż¼źŪźČźżź¾źŽź”ź╣ż└ĪŻźŪźČźżź¾źŽź”ź╣żŽVLSI└▀╝ŖĖ└Ėņż“╗╚ż├żŲRTLĮą╬üż▐żŪéb═²└▀╝ŖżŪżŁżļźūźĒĮĖ├─ĪŻAIź©ź¾źĖź╦źóż╬═ūĄßż“╩╣żŁĪóżĮżņż“éb═²ĄŁĮęż╦═Ņż╚ż╣ż│ż╚ż¼╚Óżķż╬╗┼Ą£żŪżóżļĪŻ

ż┐ż└żĘĪóAIź┴ź├źū│½╚»Ą“┼└żŪżŽĪó└▀╝Ŗź─Ī╝źļż“źóź½źŪź▀ź├ź»źŪźŻź╣ź½ź”ź¾ź╚żŪĻP(gu©Īn)Ų■żĘż┐ż┐żßĪóźŪźČźżź¾źŽź”ź╣żõ│░ŗż╬VLSI└▀╝ŖĖ└Ėņż╬Ø{įuźūźĒż╦ź─Ī╝źļż“╗╚ż’ż╣ż│ż╚żŽEDAź┘ź¾ź└Ī╝ż¼ß׿Ąż╩żżż└żĒż”Īóż╚żżż”╠mżŌ╩╣ż»ĪŻż╚żżż”ż│ż╚żŽĪóAIż╬źóźļź┤źĻź║źÓ│½╚»Ūvż┐ż┴ż¼ż│ż╬Ą“┼└ż╦═ĶżŲżŌVLSI└▀╝ŖĖ└Ėņż“Ø{įużĘĪóRTLźņź┘źļż▐żŪźūźĒź░źķźÓżĘżŲżµż½ż╩ż▒żņżąż╩żķż╩żżż╚żĘż┐żķĪóż│żņżķż╬└▀╝Ŗź─Ī╝źļżŽąg(sh©┤)ż╬Ęeż┴æžżņż╦ż╩żĻż½ż═ż╩żżČ▓żņżŌĮążŲż»żļĪŻEDAź┘ź¾ź└Ī╝ż╚Ą“┼└ż╚ż╬ÅB╣ńżżż¼ØŁ═ūżŪżóżĒż”ĪŻ

żĄżķż╦AIżŪżŽ│žØ{żĄżņż┐źŪĪ╝ź┐ż¼TensorFlowżõCaffe 2ż╩ż╔ż╬źšźņĪ╝źÓź’Ī╝ź»ż╬źšź®Ī╝ź▐ź├ź╚żŪĮ±ż½żņĪ󟻟ķź”ź╔ż╦│╩Ū╝żĄżņżŲżżżļż│ż╚ż¼¾HżżĪŻż│żņżķż╬│žØ{źŪĪ╝ź┐ż“┐õébź┴ź├źūż╦╗╚ż”ż┐żßż╦żŽĪóVLSI└▀╝ŖĖ└Ėņżžż╬╩č┤╣żõź│ź¾źčźżźļż¼ØŁ═ūż╚ż╩żļĪŻ┐õébź┴ź├źūż╦żŽż│ż╬╩č┤╣║ŅČ╚żŽ╔į▓─’L(f©źng)żŪżóżļĪŻż│ż╬║ŅČ╚ż╦┤žżĘżŲżŌAI│½╚»Ūvż╦VLSI└▀╝ŖĖ└Ėņż╬Ø{įuż“äė═ūż╣żļż│ż╚ż╦ż╩żļĪŻż│żņżŽ╠Ą═²ż¼żóżļĪŻżõżŽżĻźŪźČźżź¾źŽź”ź╣ż“AI└▀╝Ŗż╦▓║▀żĄż╗żļØŁ═ūż¼żóżļĪŻż│żņżŽ┴ߊåż╦▓“»éż“┐▐żķż╩ż▒żņżąż╩żķż╩żżż└żĒż”ĪŻ