LEAPż╬└«▓╠╩¾╣Īóż╔ż”īÖ├ōż╣żļż½Īó╠õż’żņżļ╗▓▓├┤ļČ╚

«Ć─Ń┼┼░ĄźŪźąźżź╣Č\ĮčĖ”ē|┴╚╣ńĪ╩LEAPĪ╦ż╬źūźĒźĖź¦ź»ź╚Īų─Ń├║┴Ū╝ę▓±ż“╝┬ĖĮż╣żļ«Ć─Ń┼┼░ĄźŪźąźżź╣źūźĒźĖź¦ź»ź╚ĪūżŽ╩┐└«22ŃQ┼┘ż½żķ╦▄ŃQ┼┘ż▐żŪż╬5ŃQ┤ųż╦┼Žż├żŲĖ”ē|żĄżņżŲżŁż┐ĪŻLEAPż¼╝ń╠¢ż╣żļĪųŗī4övĪĪ─Ń├║┴Ū╝ę▓±ż“╝┬ĖĮż╣żļ«Ć─Ń┼┼░ĄźŪźąźżź╣źūźĒźĖź¦ź»ź╚└«▓╠╩¾╣▓±Īūż¼ż│ż╬ż█ż╔│½ż½żņĪóżĮż╬│½╚»żĄżņż┐źŪźąźżź╣ż¼╚õŽ¬żĄżņż┐ĪŻ

┐▐1ĪĪLEAPż¼╝ń╠¢żĘż┐└«▓╠╩¾╣▓±

ź╚źķź¾źĖź╣ź┐ż╚źßźŌźĻż╬ŲDżĻ┴╚ż▀ĪĪ

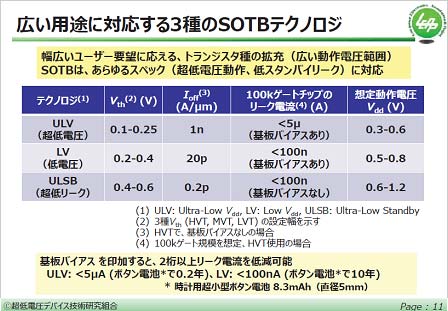

LEAPż¼5ŃQ┤ųŲDżĻ┴╚ż¾żŪżŁż┐źŲĪ╝ź▐żŽĖ▐ż─ĪŻSOTB-CMOSż╚Ō}żųź╚źķź¾źĖź╣ź┐╣Įļ]ĪóSTT-MRAMĪóPCźßźŌźĻĪóĖČ╗ęöĪŲ░Ę┐ź╣źżź├ź┴źŪźąźżź╣ĪóżĮżĘżŲź╩ź╬ź½Ī╝ź▄ź¾Ū█└■żŪżóżļĪŻSOTB-CMOSżŽĪóCMOSź╚źķź¾źĖź╣ź┐ż╬ź┴źŃź═źļōļ░Ķż╦ź╬ź¾ź╔Ī╝źū┴žż“└▀ż▒Īóź▓Ī╝ź╚żĘżŁżż┼┼░ĄVthż╬źąźķż─żŁż“žōżķżĘĪóż½ż─SOIź”ź¦Ī╝źŽż╦żĶż├żŲȧĒś┴žż“æų▓╝ż½żķżŽżĄż▀źĻĪ╝ź»┼┼╬«ż“žōżķż╣╣Įļ]ż“║╬ż├ż┐ĪŻźąźķż─żŁż“═▐ż©żļż│ż╚żŪĪó┼┼Ė╗┼┼░Ąż“▓╝ż▓żļż│ż╚ż¼żŪżŁżļĪŻ╬Ńż©żą0.2Ī┴0.4Vż╬żĘżŁżż┼┼░ĄżŪĪó0.5Ī┴0.8Vż╬Ų░║Ņ┼┼░Ąż“„[─ĻżĘĪó10╦³ź▓Ī╝ź╚ż╬æä╠Žż╬ź┴ź├źūżŪ100nA░╩▓╝ż╬źĻĪ╝ź»┼┼╬«ż“├Ż└«żĘżŲżżżļ(┐▐2)ĪŻżĄżķż╦Īó├µ└Ł╗ę└■ż╦żĶżļźĮźšź╚ź©źķĪ╝ż╦żŌźąźļź»ż╦╚µż┘3ż▒ż┐äėżżż│ż╚ż“│╬Ū¦żĘżŲżżżļĪŻ

┐▐2ĪĪSOI CMOSż╦ź╬ź¾ź╔Ī╝źū┴žż“└▀ż▒ż┐SOTBĪ╩Silicon on Thin Buried OxideĪ╦ź╚źķź¾źĖź╣ź┐ż╬└Łē”ĪĪĮąųZĪ¦LEAP

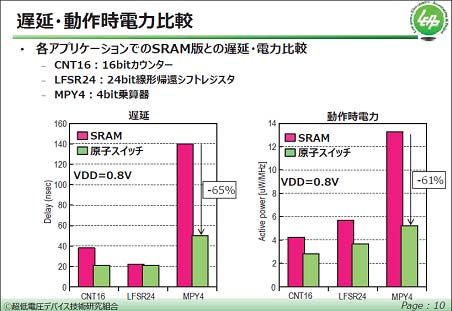

ĖČ╗ęöĪŲ░ź╣źżź├ź┴żŪżŽĪóFPGAż╩ż╔ż╬źĒźĖź├ź»ź╗źļż╬└┌żĻü÷ż©ź╣źżź├ź┴ż╚żĘżŲ╗╚ż”ż│ż╚ż“┴└ż├żŲż¬żĻĪó“£═ĶFPGAż╬ź╣źżź├ź┴ż╦╗╚ż’żņżŲżżżļSRAMż“ĖČ╗ęöĪŲ░ź╣źżź├ź┴ż╚ÅøżŁ┤╣ż©ż┐ź┴ź├źūż“║ŅżĻ╚µ│ėżĘż┐ĪŻ“£═ĶSRAMźūźĒź╗ź╣ĪóĖČ╗ęöĪŲ░ź╣źżź├ź┴źūźĒź╗ź╣ż╚żŌ65nmż╬1┴žź▌źĻźĘźĻź│ź¾Īó7┴žźßź┐źļ┴žż╬¾H┴žŪ█└■ż╬CMOSČ\Įčż“╗╚├ōżĘż┐ĪŻ1ź╗źļ┼÷ż┐żĻ2Ī▀4Ų■╬üż╬LUTĪ╩źļź├ź»źóź├źūźŲĪ╝źųźļĪ╦ż╬ź╗źļĀC└čż“╚µ│ėż╣żļż╚ĪóĖČ╗ęöĪŲ░ź╣źżź├ź┴żŽSRAMź┘Ī╝ź╣ż╬1/4ż╚ż╩ż├ż┐ĪŻ

ż▐ż┐żżż»ż─ż½ż╬SRAM┤╦▄övŽ®ż“╗Ņ║ŅżĘĪóSRAMż╚ĖČ╗ęöĪŲ░ź╣źżź├ź┴ż╚ż╬└Łē”żŌ╚µ│ėżĘż┐ĪŻ16źėź├ź╚ź½ź”ź¾ź┐żŪżŽęÆūā╗■┤ųżŽ╚ŠžōĪó4źėź├ź╚ŠĶōQ▀_żŪżŽ1/3ż╦žōż├ż┐(┐▐3)ĪŻż┐ż└żĘĪó24źėź├ź╚ż╬└■Ę┴Ąóģ▓źĘźšź╚źņźĖź╣ź┐żŪżŽż█ż╚ż¾ż╔╩čż’żķż╩ż½ż├ż┐ĪŻŲ░║Ņ┼┼╬üżŌ╚µ│ėżĘż┐ĪŻ16źėź├ź╚ź½ź”ź¾ź┐ż╚24źėź├ź╚└■Ę┴Ąóģ▓źĘźšź╚źņźĖź╣ź┐żŪżŽŲ░║Ņ╗■┼┼╬üżŽČ”ż╦2/3µć┼┘žōżĻĪó4źėź├ź╚ŠĶōQ▀_żŪżŽ1/3ż╦žōż├ż┐ĪŻČ”ż╦┼┼Ė╗┼┼░ĄżŽ0.8VĪŻĖČ╗ęöĪŲ░ź╣źżź├ź┴ż╦Ė■ż»RTLż╬éb═²╣ń└«Ī”ź▐ź├źįź¾ź░ź─Ī╝źļżŌ║Ņ└«żĘżŲżżżļĪŻĖČ╗ęöĪŲ░ź╣źżź├ź┴żŽCMOSźūźĒź╗ź╣ż╬¾H┴žŪ█└■ŗ╩¼ż╦└▀ż▒żļż┐żßĪóźūźĒź╗ź╣æųż╬ż╩żĖż▀żŽ╬╔żżżĶż”ż└ĪŻ

┐▐3ĪĪ“£═Ķż╬SRAMź┘Ī╝ź╣ż╬┤╦▄övŽ®ż╚ĪóĖČ╗ęöĪŲ░ź╣źżź├ź┴ź┘Ī╝ź╣ż╬żĮżņż╚ż╬╚µ│ėĪĪĮąųZĪ¦LEAP

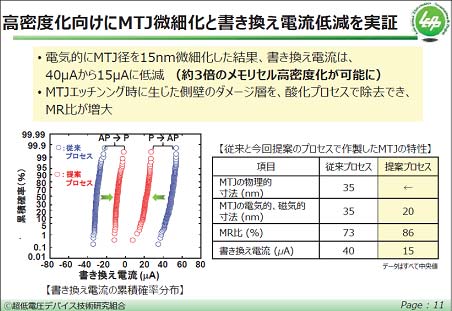

STT-MRAMżŪżŽĪó╚∙║┘▓Įż╣żļż╚MTJĪ╩╝¦Ążź╚ź¾ź═źļ└▄╣ńĪ╦ż╬Øó╦Īźąźķż─żŁż¼ĮjżŁż»ż╩żļż╚żżż”╠õ¼öż¼żóż├ż┐ĪŻżĮż│żŪ└▄╣ńż╬╝■░Žż╬Ŗõ╩╔ż“¤©▓Įż╣żļż│ż╚żŪ╝┬║▌ż╬└▄╣ńż╬─ŠĘ┬ż“╚∙║┘ż╦żĘż┐ĪŻż╣żļż╚Īóźąźķż─żŁż¼žōŠ»żĘż┐ĪŻżĮż│żŪźĻźĮź░źķźšźŻż╦żĶżļر═²Øó╦ĪżŽ35nmż╚“£═Ķż╚Ų▒żĖż╦▓├╣®żĘż╩ż¼żķżŌMTJż╬┼┼Ąż┼¬Ī”╗■┤³┼¬Øó╦Īż“35µmż½żķ20µmż╦╚∙║┘▓Įż╣żļż╚ĪóĮ±żŁ┤╣ż©┼┼╬«ż¼“£═Ķż╬40µAż½żķ15µAż╦─ŃžōżĘż┐(┐▐4)ĪŻŖõ╩╔¤©▓Įż╦ź╣źčź├ź┐ż╚śO─ś¤©▓Įż“±é├ōż╣żļż│ż╚żŪĪóźĻĪ╝ź»┼┼╬«└«╩¼żŌŠ├ż©ż┐ż╚żĘżŲżżżļĪŻ

┐▐4ĪĪ╚∙║┘▓ĮżĘżŲżŌźąźķż─żŁżŽ╗\▓├ż╗ż║Š├õJ┼┼╬«żŌ▓╝ż¼ż├ż┐ĪĪĮąųZĪ¦LEAP

16Kźėź├ź╚ż╬źßźŌźĻźóźņźżżŌ╗Ņ║ŅżĘż┐ĪŻ°BŃ^źąźķż─żŁ3”꿎ų`║Yż╬16%░╩▓╝ż“ź»źĻźõĪ╝żĘż┐ĪŻź▐ź»źĒäh▓┴├ōż╦1Mźėź├ź╚źóźņźżżŌ╗Ņ║ŅżĘżŲżżżļĪŻĮ±żŁ┤╣ż©öv┐¶ż╬▓├Å]╗Ņ┘xżŪżŽź╣ź╚źņź╣┼┼░Ąż“0.9Vż½żķ0.8VĪó0.7Vż╚▓├ż©Īó0.65VżŪżŽ10ż╬16ŠĶż╚żżż”öv┐¶ż“Ė½└čżŌż├żŲżżżļĪŻMTJżŽżĄżķż╦╝¦Ążź╗ź¾źĄż╚żĘżŲżŌŲ░║ŅżŪżŁżļż┐żßĪóźßźŌźĻż└ż▒żŪżŽż╩żż▒■├ōĖ”ē|żŌ┐╩żßżŲżżżļĪŻ

╝┬├ō▓Įż╦Ė■ż▒ż┐╠õ¼ö▓“»éżž

┴Ļ╩č▓ĮźßźŌźĻRAMżŪżŽĪóANDźšźķź├źĘźÕ╩┬ż▀ż╬Š«żĄż╩ź╗źļĀC└čżŪżóżĻż╩ż¼żķĪó“£═Ķż╬PRAMżĶżĻżŌ─ŃŠ├õJ┼┼╬üŲ░║Ņż¼żŪżŁżļTRAMż“│½╚»├µż└ĪŻPRAMżŪżŽSbĪóTeĪóGeż╬╣ńČŌż╬±TŠĮż╚ØÖŠĮ䮿╬ź╣źżź├ź┴ź¾ź░ż╦żĶż├żŲ╩čż’żļ°BŃ^ż“ŠW├ōżĘż┐ż¼ĪóTRAMżŪżŽ±TŠĮAż½żķ±TŠĮBżžż╬╔ÅöĪż“ŠW├ōż╣żļż┐żßĪóŠ├õJ┼┼╬üż¼─Ńżżż”ż©ż╦╣ŌÅ]ż╬Ų░║Ņż¼▓─ē”ż└ĪŻGeTe╦ņż╚Sb2Te3╦ņż“Ė“Ė▀ż╦▓┐┴žżŌ─_ż═╣ńż’ż╗żļĪų«Ć│╩╗ęĪūż“║ŅżļĪŻżĮż╬±T▓╠Īó“£═Ķż╬PRAMż╚╚µż┘Īó┼┼Ė╗┼┼░ĄżŽ40%ż╦▓╝ż¼żĻĪóŠ├õJ┼┼╬«żŽ╚ŠžōżĘż┐ĪŻ1M/2Mż╬ź▐ź»źĒż“╗Ņ║ŅżĘŲ░║Ņż“│╬Ū¦żĘżŲżżżļż¼ĪóŁé▀`ż╦żĶżļ╣Ō°BŃ^╔į╬╔ż¼╚»Ö┌żĘżŲż¬żĻĪóż│żņż“▓“»éż╣żļØŁ═ūż¼żóżļĪŻ

║ŪĖÕż╦ź╩ź╬ź½Ī╝ź▄ź¾Ū█└■ż└ż¼Īó═ūĄßżŽŲ¾ż─żóżļĪŻ▐kż─żŽĪóCuŪ█└■ż“╚∙║┘▓Įż╣żļż╚Ū█└■ż╬źĘĪ╝ź╚°BŃ^ż¼Šå╗\żĘżŲżżż»╠õ¼öż“▓“»éżŪżŁżļż│ż╚ĪŻżŌż”▐kż─żŽĪó3╝ĪĖĄNANDźšźķź├źĘźÕż╬żĶż”ż╦╣Ōżżźóź╣ź┌ź»ź╚╚µż╬Ų│─╠Ū█└■ż¼Ąßżßżķżņżļż│ż╚ż└ĪŻź│ź¾ź┐ź»ź╚ź█Ī╝źļżõTSVż“ļmżßżļż╬ż╦ź╩ź╬ź½Ī╝ź▄ź¾ż¼Ė■ż»ĪŻ▓ŻöĄĖ■ż╬Ū█└■ż╦żŽ¾H┴žź░źķźšź¦ź¾ż“╗╚żżĪóāeöĄĖ■ż╬Ū█└■ż╦żŽCNTĪ╩ź½Ī╝ź▄ź¾ź╩ź╬ź┴źÕĪ╝źųĪ╦ż“╗╚żż╩¼ż▒ż╣żļĪŻź╩ź╬ź½Ī╝ź▄ź¾Ū█└■╠®┼┘ż¼ż▐ż└─Ńżżż¼Īó300mmź”ź¦Ī╝źŽż╦Ę┴└«ż╣żļż╚żżż”╝┬┘xż“╣įż├ż┐ĪŻ

ż│żņżķż╬└«▓╠ż“Įą½@▓±╝ęż¼Ö┌ŠÅźķźżź¾ż╦║▄ż╗żļż│ż╚ż¼żŪżŁżļż╚Īó┐Ęż┐ż╦×æēä│½╚»ż╣żļżĶżĻżŌź│ź╣ź╚ż“═▐ż©żķżņżļĪŻżŌż┴żĒż¾ĪóżĘż├ż½żĻżĘż┐ź▐Ī╝ź▒źŲźŻź¾ź░ż¼─_═ūżŪĪóĖ▄Ąę│½¹£ż“ź©ź¾źĖź╦źóż¼śOżķ╣įż’ż╩ż▒żņżąż╩żķż╩żżĪŻżĮż╬ż┐żßż╬┼Ļ½@żŌØŁ═ūż└ż¼Īó┬Šż╬×æēä│½╚»żŪżŌŲ▒══ż╩┼Ļ½@ż¼ż½ż½żļż╚╣═ż©żļż╬ż╩żķĪó±TČ╔ĪóīÖ├ōż╣żļöĄż¼ROIżŽŃ~ŠWżŪżŽż╩żżż└żĒż”ż½ĪŻ