2039ŃQż╦Ė■ż▒ż┐źĒźĖź├ź»źŪźąźżź╣╚∙║┘▓ĮźĒĪ╝ź╔ź▐ź├źū║Ū┐Ę╚Ūż“Ų╔ż▀▓“ż»

ź┘źļź«Ī╝ż╬└ż─c║Ū└Ķ├╝╚ŠŲ│öüĖ”ē|ĄĪ┤žżŪżóżļimecżŽĄŅżļ5ĘŅ▓╝Į▄ż╦┴Ž╬®40╝■ŃQĄŁŪ░źżź┘ź¾ź╚ĪųITFĪ╩imec Technology ForumĪ╦World 2024Īūż“ź┘źļź«Ī╝Ī”źóź¾ź╚ź’Ī╝źūżŪ│½╠¢żĘż┐ĪŻżĮż╬┤─┤╣ų▒ķżŪĪóŲ▒╝ęCEOż╬Luc Van den hoveĢ■Ī╩┐▐1Ī╦ż¼ĪóźĒźĖź├ź»źŪźąźżź╣╚∙║┘▓Įż╬źĒĪ╝ź╔ź▐ź├źū2024ŃQ║Ū┐Ę╚Ūż“╚»╔ĮżĘż┐ĪŻżĄżķż╦ĪóimecżŽĪóEUżõź┘źļź«Ī╝Ī”źšźķź¾ź└Ī╝ź╣Ž×ĮBż╬▌öÕ\ČŌż¬żĶżė░c┤ų┤ļČ╚ż╬Įą½@ČŌĪó┴Ē±Y╠¾4200▓»▀ģżŪĪó2nmż¬żĶżėżĮżņ░╩▓╝ż╬źŪźąźżź╣ż╬╗Ņ║Ņźķźżź¾ż“Ę·└▀ż╣żļż│ż╚ż“╚»╔ĮżĘż┐ĪŻŲ▒╝꿎Īó╚ŠŲ│öü═ū┴ŪČ\Įč│½╚»ż└ż▒żŪżŽż╩ż»ĪóźĒĪ╝ź╔ź▐ź├źūż“śOżķ╝┬Š┌ż╣żļż┐żßĪó╗Ņ║ŅżõŠ»╬╠Ö┌ŠÅż▐żŪŠ}²Xż▒żļ╠Ž══żŪżóżļĪ╩╗▓╣═½@╬┴1Ī╦ĪŻ

┐▐1ĪĪ┤─┤╣ų▒ķż╣żļimec CEOż╬Luc Van den hoveĢ■ĪĪĮąųZĪ¦ITF World 2024ż╦żŲ╔«Ūv╗Ż▒Ų

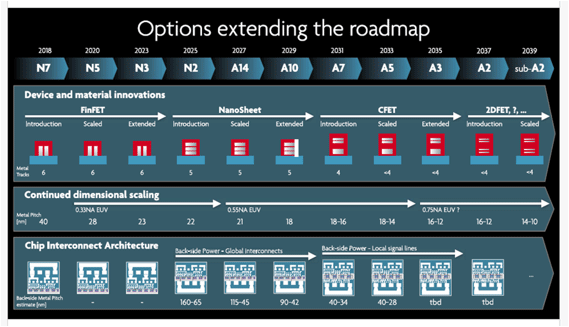

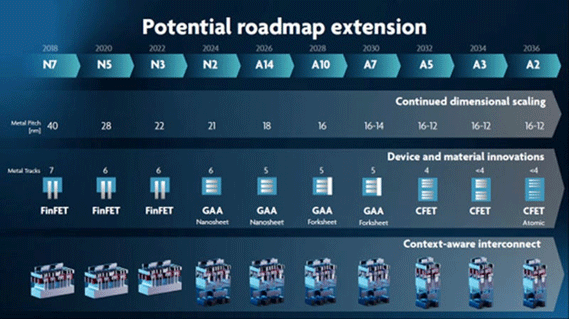

imecż¼┐Ęż┐ż╦╚»╔ĮżĘż┐źĒĪ╝ź╔ź▐ź├źūż╦żŽĪó15ŃQ└Ķż╬2039ŃQż╬Sub-A2 Ī╩żżż’żµżļ2Å«Ćż╬Č\Įčź╬Ī╝ź╔Ī╦ż╬╝Ŗ▓Ķż▐żŪ“EżĻ╣■ż▐żņżŲżżżļ(┐▐2╗▓Š╚)ĪŻ│½Ė²╬©NAĪß0.75ż╬hyper NA Ī╩«Ć╣ŌNAĪ╦EUVźĻźĮź░źķźšźŻżõ2Dź┴źŃź═źļ║Ó╬┴żõź┴ź├źūż╬╬óĀC┼┼Ė╗ČĪĄļėæżõ╔Į╬ó╬ŠĀCżžż╬┼┼Ąż┐«ęÄėæŪ█Åøż╩ż╔ż╬▓Ķ┤³┼¬ż╩Č\Įčż¼┤▐ż▐żņżŲżżżļĪŻż│żņżķż“Š▄żĘż»Ė½żŲżżż│ż”ĪŻ

┐▐2ĪĪimecż¼ITF World 2024ż╦żŲ╚»╔ĮżĘż┐źĒźĖź├ź»źŪźąźżź╣ż╬╚∙║┘▓ĮźĒĪ╝ź╔ź▐ź├źūĪĪź┐źżź╚źļżŽĪųźĒĪ╝ź╔ź▐ź├źūż“Įø═Ķżž│╚─źż╣żļż┐żßż╬┬ō┘I╗ĶĪūż╚ż╩ż├żŲżżżļĪŻĪĪĮąųZĪ¦imecĪó2024ŃQ5ĘŅ

ź╚źķź¾źĖź╣ź┐╣Įļ]ż╦┤žżĘżŲżŽĪóN3 Ī╩żżż’żµżļ3nmČ\Įčź╬Ī╝ź╔Ī╦ż▐żŪżŽFinFETż¼╗╚ż’żņżļż¼Īó2025ŃQ╬╠ŠÅ│½╗Ž═Į─Ļż╬N2ż½żķżŽźĘźĻź│ź¾Ī”ź╩ź╬źĘĪ╝ź╚ż“║╬├ōżĘż┐Gate-All-Around╣Įļ]ż¼Ų│Ų■żĄżņżļĪ╩ÅR1Ī╦ĪŻ2031ŃQż╬A7ż½żķżŽnź┴źŃź═źļGAAź╚źķź¾źĖź╣ź┐ż╚pź┴źŃź═źļGAAź╚źķź¾źĖź╣ź┐Ė“Ė▀ż╦└č┴žżĘż┐CMOS╣Įļ]ż╬CFET(┴Ļ▌öĘ┐FET)Ī╩╗▓╣═½@╬┴2Ī╦ż¼║╬├ōżĄżņżļĪŻżĮż╬ĖÕĪó2D FET(2╝ĪĖĄ║Ó╬┴ż“ź┴źŃź═źļōļ░Ķż╦║╬├ōżĘż┐FETĪ╩ÅR2)żŽżĖżßĪóż▐ż├ż┐ż»┐ʿʿż║Ó╬┴Ī”╣Įļ]ż“║╬├ōżĘż┐FETż¼┼ąŠņż╣żļĖ½╣■ż▀żŪżóżļĪŻ

ż▐ż┐Īóŗī1┴žźßź┐źļż╬źčź┐Ī╝ź╦ź¾ź░ż╦┤žżĘżŲżŽĪó2025ŃQż▐żŪżŽĪóNA=0.33ż╬EUVŽ¬Ė„äóÅøż╦żŲźßź┐źļźįź├ź┴22nmż▐żŪźčź┐Ī╝ź╦ź¾ź░ĪóżĮżņ░╩æTżŽNA=0.55ż╬╣ŌNA EUVż╦öĪ╣įż╣żļż╚żĘż┐ż█ż½Īóźßź┐źļźįź├ź┴16-12nm░╩æTżŽĪó╩Ōé╬ż▐żĻ─Ń▓╝ż“żŌż┐żķż╣ź└źųźļźčź┐Ī╝ź╦ź¾ź░ż“ķcż▒źĘź¾ź░źļźčź┐Ī╝ź╦ź¾ź░ż“╣įż”ż┐żßż╦żŽNA=0.75ż╬«Ć╣ŌNA EUVż╦öĪ╣įż╣żļØŁ═ūż¼żóżļż╚ż╬Ė½öĄż“┐āżĘżŲżżżļĪŻ

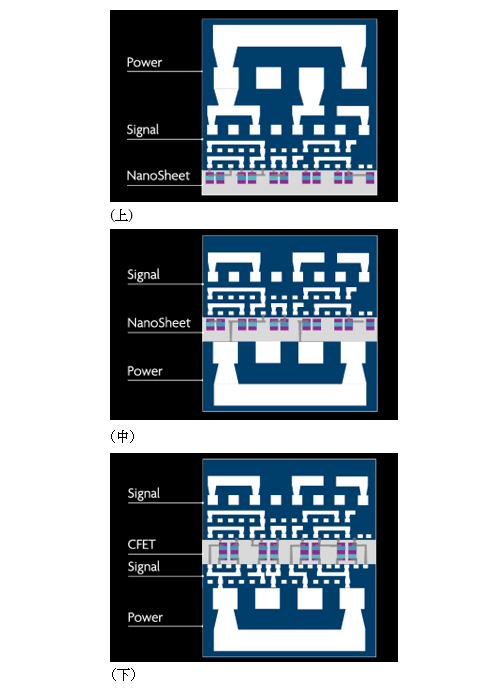

źżź¾ź┐Ī╝ź│ź═ź»ź╚ż╦┤žżĘżŲżŽĪó2025ŃQĪ╩N2Ī╦ż╬ź╩ź╬źĘĪ╝ź╚ż½żķżŽ╬óĀC┼┼Ė╗ČĪĄļėæż“║╬├ōżĘĪó╔ĮĀCż╬┼┼Ąż┐«ęÄėæż╬╚∙║┘▓Įż“┐╩żßżļĪŻ2031ŃQĪ╩A7Ī╦ż╬CFETżŪżŽĪó╬óĀC┼┼Ė╗ČĪĄļėæż╦▓├ż©żŲĪó┼┼Ąż┐«ęÄėæż╬▐kŗżŌ╬óĀCż╦öĪżĘĪó╔Į╬ó╬ŠĀCż½żķ┼┼Ąż┐«ęÄż“┼┴┴„ż╣żļĪŻż│ż╬╩šż╬ėXČĘż“╠Ž╝░┐▐żŪ└Ō£½żĘżĶż”ĪŻ

┐▐3Ī╩æųĪ╦żŽĪó“£═Ķż½żķż╬źżź¾ź┐Ī╝ź│ź═ź»ź╚Ū█ÅøżŪĪó┼┼Ė╗ČĪĄļėæż╚┐«ęÄŪ█└■ėæż¼źĘźĻź│ź¾┤łŖõż╦║«║▀żĘżŲżżżļĪŻ┐▐3Ī╩├µĪ╦żŽĪó┼┼Ė╗ČĪĄļėæż“╬óĀCż╦öĪŲ░żĄż╗Īó╔ĮĀCżŽ┐«ęÄŪ█└■ėæż└ż▒ż╦ż╣żļŪ█ÅøżŪź╚źķź¾źĖź╣ź┐żõŪ█└■╠®┼┘ż“æųż▓żļż│ż╚ż¼żŪżŁżļĪŻ┐▐3Ī╩▓╝Ī╦żŽĪóNź┴źŃź¾ź═źļFETż╚Pź┴źŃź¾ź═źļFETż“└č┴žżĘż┐CFET║╬├ōż╦╚╝żżĪó╬óĀC┼┼Ė╗ČĪĄļėæż╦▓├ż©żŲĪó┐«ęÄŪ█└■ėæż╬▐kŗżŌ╬óĀCż╦Ū█ÅøżĘĪó┐«ęÄŪ█└■ėæż“╔Į╬ó╬ŠĀCż╦Ū█Åøż╣żļż╚żżż”╣Į„[żŪżóżļĪŻ

┐▐3ĪĪźżź¾ź┐Ī╝ź│ź═ź»ź╚Ū█Åøż╬┐╩▓Į═Į▒RĪĪ(æų)┼┼Ė╗ČĪĄļėæż╚┐«ęÄŪ█└■ėæż¼źĘźĻź│ź¾┤ł╔ĮĀCŖõż╦Ūč┘VżĄżņż┐“£═Ķż½żķż╬╣Įļ]ĪóĪ╩├µĪ╦┼┼Ė╗ČĪĄļėæż“źĘźĻź│ź¾┤ł╬óĀCż╦Ū█ÅøżĘĪó╔ĮĀCŖõż╬┐«ęÄŪ█└■ėæż╦╠®┼┘ż“æųż▓żļ╣Įļ]Ī╩2025ŃQ║óĪ®Ī╦ĪóĪ╩▓╝Ī╦CFETż╬┼ąŠņż╦ż╚żŌż╩żż┐«ęÄŪ█└■ėæż╬▐kŗżŌ╬óĀCż╦Ū█ÅøżĘż┐╣Įļ]Ī╩2031ŃQ║óĪ®Ī╦ĪĪĮąųZĪ¦imec

ASMLżŽ«Ć╣ŌNA EUVźĻźĮź░źķźšźŻäóÅøż“│½╚»├µ

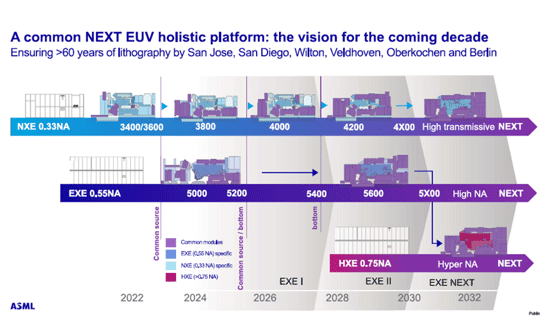

ITF World 2024żŪżŽĪó─╣ŃQż╦ż’ż┐żļimecż╬źĻźĮź░źķźšźŻĖ”ē|│½╚»źčĪ╝ź╚ź╩Ī╝żŪżóżļASMLż╬Øi╝ę─╣Ę¾CTOż╬Martin van den BrinkĢ■ż¼Īó│½Ė²┐¶NA=0.75ż╬«Ć╣ŌNA EUVŽ¬Ė„äóÅøż“│½╚»├µżŪżóżļż│ż╚ż“£½żķż½ż╦żĘż┐ĪŻ

NA=0.75ż╬«Ć╣ŌNA EUVźĘź╣źŲźÓżŽĪóIntelż¼┬Š╝ęż╦└ĶŅ~ż▒żŲ2023ŃQ¼Źż╦Ų│Ų■żĘż┐NA=0.55ż╬╣ŌNA EUVŽ¬Ė„äóÅøż╬ĖÕ┘Mż╦░╠Åøż┼ż▒żķżņżļżŌż╬żŪżóżļĪŻż┴ż╩ż▀ż╦ĪóŲ³╦▄ż╬ĪĪ╣±║÷źķźįź└ź╣ż¼Īó═ĶŃQĪó╗h║ą╣®Šņż╦Ų│Ų■żĘżĶż”ż╚żĘżŲżżżļEUV źĻźĮź░źķźšźŻäóÅøżŽĪóNAĪß0.33ż╬“£═ĶĄĪżŪżóżļĪŻ

┐▐4ĪĪASMLż╬EUVźĻźĮź░źķźšźŻäóÅøĘQźŌźŪźļż╬Įą▓┘źĒĪ╝ź╔ź▐ź├źūĪĪĮąųZĪ¦ASML

imecż╬┐Ęż┐ż╩źĒĪ╝ź╔ź▐ź├źūż╦Ō}▒■żĘżŲĪóASMLżŽĪóITFĪĪWord 2024żŪĪó║ŻĖÕż╬EUVźĻźĮź░źķźšźŻäóÅøĪ╩╗Ņ║ŅĖĪŲżźŌźŪźļż¬żĶżė╬╠ŠÅźŌźŪźļĪ╦ż╬Įą▓┘źĒĪ╝ź╔ź▐ź├źūż“┐āżĘż┐Ī╩┐▐4Ī╦ĪŻ┐▐ż╬æų├╩żŽĪó“£═Ķż╬│½Ė²┐¶NA=0.33ż╬äóÅøż╬ĘQźŌźŪźļż╬Įą▓┘╝Ŗ▓ĶĪó├µ├╩ż¼ĪóNA=0.55ż╬╣ŌNAĪĪEUVäóÅøĪó▓╝├╩ż¼NA=0.75ż╬«Ć╣ŌNA EUVäóÅøż╬Įą▓┘╝Ŗ▓ĶżŪżóżļĪŻ

░╩Øiż╬źĒĪ╝ź╔ź▐ź├źūżŪżŽN3╬╠ŠÅ╗■┤³ż¼2022ŃQż└ż├ż┐ż¼╝┬║▌żŽ23ŃQ

░╩æųŠę▓żĘż┐imecż╬źĒźĖź├ź»╚∙║┘▓ĮźĒĪ╝ź╔ź▐ź├źūż“2ŃQØiż╬źĒĪ╝ź╔ź▐ź├źūĪ╩┐▐2Ī╦ż╚╚µ│ėżĘżŲż▀żĶż”ĪŻĄņ╚ŪĪ╩2022ŃQ╚ŪĪ╦żŪżŽĪóN3ż╬╬╠ŠÅ│½╗ŽżŽ2022ŃQż╦ż╩ż├żŲżżż┐ż¼Īó╝┬║▌żŽ2023ŃQż╦ż╩ż├żŲżĘż▐ż┐ż┐żßĪó┐Ę╚ŪżŪżŽĪóżĮżņ░╩æTż╬╝Ŗ▓Ķż“1ŃQĖÕż║żĄżĻżĄż╗żŲżżżļĪŻĄņ╚ŪżŪżŽĪóź╩ź╬źĘĪ╝ź╚GAAż╚CFETż╬┤ųż╦ĪóA10ż╚A7żŪżŽźšź®Ī╝ź»źĘĪ╝ź╚GAAż¼┼ąŠņż╣żļż╚żĘżŲżżż┐ż¼ĪóŠ├ż©żŲżĘż▐ż├ż┐ĪŻ┐Ę╚ŪĪ╩2024ŃQ╚ŪĪ╦żŪżŽĪóź╩ź╬źĘĪ╝ź╚ż¼A10ż▐żŪūā╠┐ż╣żļż╚ż╚żŌż╦ĪóĄņ╚ŪżŪżŽĪóA5Ī╩2032ŃQĪ╦ż½żķż╚ż╩ż├żŲżżż┐CFETż¼Īó┐Ę╚ŪżŪżŽA7Ī╩2031ŃQĪ╦ż½żķż╚Øi┼▌żĘż╦ż╩ż├żŲżżżļĪŻĄņ╚ŪżŪżŽĪó┐«ęÄŪ█└■ėæż╬▐kŗż“╬óĀCŖõż╦öĪż╣╣Į„[żŌż▐ż└┼ąŠņżĘżŲżŽżżż╩ż½ż├ż┐ĪŻ

ż│ż╬żĶż”ż╦ĪóźĒĪ╝ź╔ź▐ź├źūżŽ2ŃQż╬┤ųż╦══Ī╣ż╩╩čśŗż¼żĄżņżŲżżżļĪŻ╚∙║┘▓ĮżŽż▐ż╣ż▐ż╣žMżĘż»ż╩ż├żŲżŁżŲżżżļż╬żŪĪó║ŻĖÕ15ŃQż╦ż’ż┐żĻĪó╚∙║┘▓Įż╬Č\Įčź╬Ī╝ź╔ż¼Įń─┤ż╦2ŃQż┤ż╚ż╦Øi┐╩ż╣żļż╬żŽ║żžMż╚╗ūż’żņĪóźĒĪ╝ź╔ź▐ź├źūżŽ▓┐┼┘żŌT┘ćż“Ę½żĻ╩ųż╣▓─ē”└Łż¼╣ŌżżĪ╩┐▐5Ī╦ĪŻ

┐▐5ĪĪimecż¼ITF World 2022ż╦żŲ╚»╔ĮżĘż┐źĒźĖź├ź»źŪźąźżź╣ż╬╚∙║┘▓ĮźĒĪ╝ź╔ź▐ź├źūĪĪź┐źżź╚źļżŽĪųźĒĪ╝ź╔ź▐ź├źūż╬Įø═Ķżžż╬│╚─źż╬Ė½╣■ż▀Īūż╚ż╩ż├żŲżżżļĪŻĪĪĮąųZĪ¦imecĪó2024ŃQ5ĘŅ

░╩ØiĪó╣±║▌╚ŠŲ│öüČ\ĮčźĒĪ╝ź╔ź▐ź├źūĪ╩ITRSĪóĖĮ║▀żŽIRDSż╦▓■┴╚Ī╦ż╬źĘź¾ź▌źĖź”źÓżŪĪóĪųż╩ż╝źĒĪ╝ź╔ź▐ź├źūżŽ╦ĶŃQśŗ┐Ęż╣żļż╬ż½Īūż╚ż╬▓±Šņż½żķż╬ä®╠õż╦Īó░čµ^─╣ż¼Īų╚ŠŲ│öüČ\Į迎Īó1ŃQ└ĶżĄż©┘ćżĘż»═Į▒RżŪżŁż╩żżėXČĘż╩ż╬żŪ╦ĶŃQT┘ćż╣żļØŁ═ūż¼żóżļż½żķĪūż╚┼·ż©żŲżżż┐ż╬ż“╗ūżżĮążĘż┐ĪŻ

źĒĪ╝ź╔ź▐ź├źūżŽżóż»ż▐żŪżŌ┤Ļ╦Šż“╣■żßż┐ż┐ż┐żŁ±śż└ĪŻŪ╦Žs┼¬źżź╬ź┘Ī╝źĘźńź¾ż“żŌż┐żķż╣Īó═Į▒RżĘįuż╩ż½ż├ż┐żĶż”ż╩╗┬┐Ęż╩źóźżźŪźóż¼┼ąŠņżĘĪóżĮż╬╝┬├ō▓ĮżŪ┐Ęż┐ż╩╠ż═Ķż¼¹£ż½żņżļż│ż╚ż“┤³┬įżĘż┐żżĪŻ

ÅRłį

1. N2ż½żķź╩ź╬źĘĪ╝ź╚║╬├ōĪ¦ż│żņżŽĪóTSMCż╬źĒĪ╝ź╔ź▐ź├źūż╦żĶżļĪŻż╩ż¬ĪóimecżŽĪó▓żä”├Ž░Ķż╬TSMC Design Alliance Ī╩TDAĪ╦ż╦╗žć@żĄżņżŲż¬żĻĪó└▀╝ŖźļĪ╝źļż“Č”─╠▓ĮżĘżŲżżżļĪŻimecżŽĪó▓żä”ż╬Ė▄Ąęż¼TSMCżžŠ»╬╠Ö┌ŠÅż“░č▓mż╣żļ║▌ż╬ÄXĖ²ż╚ż╩ż├żŲż¬żĻĪóTSMCż╚żŽżŁż’żßżŲ┐ŲżĘżżĪŻ▐köĄĪóSamsungĪĪElectronicsżŽĪóTSMCż╦└Ķ╣įżĘżŲż╣żŪż╦SF3 Ī╩imec/TSMCż╬N3┴Ļ┼÷Ī╦ż½żķź╩ź╬źĘĪ╝ź╚ż“║╬├ōżĘż┐ż¼Īó╩Ōé╬ż▐żĻ─Ń╠┬żŪ∙Z└’żĘż┐ĪŻ

2. 2D║Ó╬┴Ī¦╔ÅöĪČŌō’Ī╩Transition MetalĪ╦ż╚ź½źļź│ź▓ź╩źżź╔Ī╩ChalcogenideĪ╦ż╬▓Į╣ńرżŪżóżļĪų╔ÅöĪČŌō’ź└źżź½źļź│ź▓ź╩źżź╔Ī╩TMDĪ╦Īūżõź░źķźšź¦ź¾ż╩ż╔ż╬1Ī┴┐¶ĖČ╗ę┴žż╬Ī╩Ė³ż▀ż╬ż╩żż2╝ĪĖĄż╬Ī╦╣ŌöĪŲ░┼┘ź┴źŃź═źļ║Ó╬┴ĪŻ

╗▓╣═½@╬┴

1. └Kŗō·ĪóĪųimecż¼2nm░╩▓╝ż╬SoC╗Ņ║Ņźķźżź¾ż“Ę·└▀żžĪó┼Ļ½@┴Ē±Y╠¾4200▓»▀ģż“═Į─ĻĪūĪóź▐źżź╩źėź╦źÕĪ╝ź╣TECH+Īó(2024/05/22)

2. ╦┘Ė²─Š┐═ż█ż½ĪóĪųźĒźĖź├ź»źŲź»ź╬źĒźĖż╬źĒĪ╝ź╔ź▐ź├źūż╦┼ąŠņżĘż┐ē|Č╦ż╬ź╚źķź¾źĖź╣ź┐ĪžCFETĪ┘ĪūĪżź▐źżź╩źėź╦źÕĪ╝ź╣TECH+Īó(2023/05/11)