TSMCż¼±śŽčżŪ╝ĪĪ╣ż╚Ę·└▀ż╣żļ "Advanced" Backend Fabż╚żŽ▓┐Ī®

Øiövż╬źųźĒź░Ī╩╗▓╣═½@╬┴1Ī╦żŪĪóTSMCż╬±śŽč░ĶŲŌż└ż▒żŪżŽż╩ż»ź░źĒĪ╝źąźļż╩źšźĪźų▐k═„ż“┐āżĘż┐ż¼Īó╝┬żŽż│żņż¼TSMCż╬źšźĪźųż╬ż╣ż┘żŲżŪżŽż╩żżĪŻØiövŠę▓żĘż┐ż╬żŽĪóØi╣®µćĪ╩FrontendĪ󟔟¦Ī╝źŽźūźĒź╗ź╣╣®µćĪ╦ż╬źšźĪźųż└ż▒żŪżóż├żŲĪó╝┬żŽĪų└Ķ┐╩┼¬ż╩ĖÕ╣®µćĪūĪ╩└Ķ┐╩źóź├ź╗ź¾źųźĻż╚║ŪĮ¬źŲź╣ź╚Ī╦ż╬źšźĪźųż¼░╩▓╝ż╬żĶż”ż╦±śŽčŲŌż╬5ź§ĮĻż╦┼└║▀żĘżŲżżżļĪŻż│żņżķż╬┘J┘TźšźĪźųż╚żŽ╩╠ż╦║ŻĖÕżĄżķż╦2ż─ż╬źšźĪźųż“╗\└▀ż╣żļĖ½╣■ż▀żŪżóżļĪŻ

┘J┘T╣®Šņ

Advanced Backend Fab 1ĪĪ±śŽčĪ”┐Ęāń

Advanced Backend Fab 2ĪĪ±śŽčĪ”±śŲŅ

Advanced Backend Fab 3ĪĪ±śŽčĪ”┼ĒŠÄĪĪĪ╩┐Ęāń▌xż╬Ē×öĄĪ╦

Advanced Backend Fab 5ĪĪ±śŽčĪ”±ś├µ

Advanced Backend Fab 6ĪĪ±śŽčĪ”āńŲŅĪĪĪ╩┘ĀʬĖ®Ī╦║Ū└Ķ├╝µ£śOŲ░×æļ]źķźżź¾

╝Ŗ▓Ķ├µż╬╣®Šņ

(Advanced Backend Fab 7)ĪĪ±śŽčĪ”Ų╝’š(ż╔ż”żķ)Ī╩┘ĀʬĖ®Ī╦ĪĪ2024ŃQŠÆ╣®

(Advanced Backend Fab 8)ĪĪ±śŽčĪ”▓┼▒IĖ®ż½Ų▐╬ėĖ®ĪĪĖĪŲż├µ

┐▐1ĪĪ2023ŃQ╔nŲ»ż╬║Ū┐Ęż╬TSMC Advanced Backend Fab 6ĪĪĮąųZĪ¦TSMC

Fab 4 ż¼’L╚ųż╦ż╩ż├żŲżżżļż╬żŽĪóØiöv└Ō£½żĘż┐żĶż”ż╦ĪóŲ³╦▄ĖņŲ▒══ż╦├µ╣±ĖņżŪżŌ4żŽ┤„ż▀┐¶ż└ż½żķżŪżóżļĪŻ

TSMCżŽĪó├▒ż╦Backend Fab (ĖÕ╣®µć╣®Šņ)ż╚Ė└ż’ż║ż╦Ī󿒿ȿ’żČĪųAdvanced Ī╩└Ķ┐╩┼¬Ī╦Īūż“ż─ż▒żŲżżżļż╬ż└żĒż”ż½Ī®±śŽčż╦żŽ¾H┐¶ż╬ĖÕ╣®µć£p▓m└ņ╠ńČ╚ŪvOutsourced Semiconductor Assembly and TestĪ╩OSATĪ╦ż¼┘T║▀żĘĪóØi╣®µć├┤┼÷ż╬źšźĪź”ź¾ź╔źĻż╚╩¼Č╚żĘżŲżŁż┐ĪŻżĘż½żĘĪó3D-ICż╬┼ąŠņżŪĖÕĮęż╣żļżĶż”ż╦Øi╣®µćż╚ĖÕ╣®µćż╬ČŁ─cż¼żóżżż▐żżż╚ż╩ż├ż┐æųż╦ĪóŲ╚śO│½╚»ż╬3D-ICźóź╗ź¾źųźĻČ\Įčż╬╚ļ╠®╩▌Ęeż╬ż┐żßż╦Īó└Ķ├╝źŪźąźżź╣ż╦┤žżĘżŲżŽĪóźšźĪź”ź¾ź╔źĻż¼ĖÕ╣®µćżŌŲŌ×æ▓Įż╣żļżĶż”ż╦ż╩ż├żŲżŁżŲżżżļĪŻ

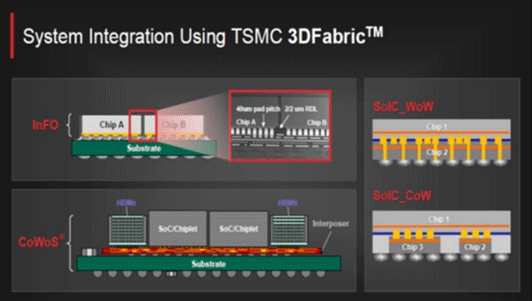

Advanced Backend Fabż╬ż”ż┴Īó║ŪżŌ┐ʿʿż╗▄└▀żŽāńŲŅźĄźżź©ź¾ź╣źčĪ╝ź»ż╦2023ŃQ6ĘŅż╦│½ĮĻżĘż┐żąż½żĻż╬Advanced Package Fab 6Ī╩┐▐1Ī╦żŪĪóŲ▒╝ęż╬3DĪ╩3╝ĪĖĄĪ╦╝┬äóČ\ĮčĪų3DFabricĪūĪ╩┐▐2Ī╦Ī╩╗▓╣═½@╬┴2Ī╦ż╦×┤▒■ż╣żļĮķż╬µ£śOŲ░▓Įźčź├ź▒Ī╝źĖź¾ź░Ī┐źŲź╣ź╚╣®Šņż╚ż╩ż├żŲżżżļĪŻż─ż»żąż╬TSMC 3D R&D Centerż╬ź»źĻĪ╝ź¾źļĪ╝źÓĪ╩┐▐2Ī╦żŽĪó±śŲŅż╬Advanced Backend Fab 6ż╚ź│źįĪ╝źżź░źČź»ź╚źĻż╬źņźżźóź”ź╚ż╦ż╩ż├żŲż¬żĻĪóż─ż»żążŪż╬Ė”ē|└«▓╠ż“żĮż╬ż▐ż▐±śŽčż╬╣®Šņż╦öĪ┤╔żŪżŁżļżĶż”ż╦ż╩ż├żŲżżżļż╚Ė└ż’żņżŲżżżļĪŻ

┐▐2ĪĪTSMCż╬3D╝┬äóż╬┴ĒŠ╬żŪżóżļ3D FabricĪĪĮąųZĪ¦TSMC

└Ķ┐╩ĖÕ╣®µćż╬ź»źĻĪ╝ź¾źļĪ╝źÓŲŌŗżŽ▐k└┌Įo│½żĄżņżŲżżż╩żżż¼Īóż─ż»żąż╬TSMC 3D-IC R&D Centerż╬ļA╣®─ŠĖÕż╬äóÅø╚┬Ų■Øiż╬└^┐┐ż¼Ż▒ĮŚż└ż▒źßźŪźŻźóż╦Įo│½żĄżņżŲżżżļż╬żŪż┤═„ż╦ż╩żķżņż┐öĄżŌ¾Hżżż└żĒż”Ī╩┐▐3╗▓Š╚Ī╦ĪŻØi╣®µćŲ▒══ż╬ź”ź¦Ī╝źŽ╝²Ū╝ź▄ź├ź»ź╣śOŲ░╚┬┴„źĘź╣źŲźÓż¼ÜW░µ─źżĻĮõżķżĄżņżŲżżżļĪŻØiĮężĘż┐żĶż”ż╦Ī󱜎čż╬║Ū└Ķ├╝ż╬Advanced Backend Fabż╚ź│źįĪ╝źżź░źČź»ź╚źĻż╬źņźżźóź”ź╚ż╚äóÅø╣Į└«ż╦ż╩ż├żŲżżżļż┐żßĪóŗ│░Ūvż╬╬®ż┴Ų■żĻżõ└^┐┐╗Ż▒ŲżŽß×▓─żĄżņżŲżżż╩żżĪŻ

┐▐3ĪĪż─ż»żąż╬TSMC 3D-IC R&D Center ź»źĻĪ╝ź¾źļĪ╝źÓŲŌŗĪĪĮąųZĪ¦TSMC

ĮĖ└čövŽ®ż¼2.5DĪóśŗż╦żŽ3D▓Įż╣żļż╦ż─żņżŲĖÕ╣®µćżŌ╣Ō┼┘▓ĮżĘżŲżŁżŲĪ󟻟ĻĪ╝ź¾źļĪ╝źÓż╬╦{Š¶┼┘żŌ×æļ]äóÅøżŌØi╣®µć╩┬ż▀ż╚ż╩żĻĪó×æļ]ż╦╗╚├ōżĄżņżļ×æļ]äóÅøżŌØi╣®µć├ōż¼▐kŗ┼Š├ōżĄżņżļżĶż”ż╦ż╩ż├żŲżŁż┐ż┐żßĪóśŗż╦żŽ╩Ż┐¶ż╬ź┴ź├źūż“└▄¶öż╣żļ╣Ō┼┘ż╩źūźĒź╗ź╣Č\Įčż╬╚ļ╠®╩▌Ęeż╬ż┐żßż╦ĪóźšźĪź”ź¾ź╔źĻżŌ└Ķ├╝×æēäż╦┤žżĘżŲżŽŲ╚śOż╬ĖÕ╣®µć╣®ŠņĪ╩Advanced Backend FabĪ╦ż“Ę·└▀ż╣żļżĶż”ż╦ż╩ż├ż┐ĪŻTSMCżŽĪóAIź┴ź├źūĖ■ż▒CoWoSĪ╩ÅRĪ╦źūźĒź╗ź╣ż╬Ö┌ŠÅē”╬üż¼ŠåŚ„ż╩ęŖ═ū╗\▓├ż╦×┤▒■żŪżŁżŲżżż╩żżż┐żßĪó▐kŗż“│░ŗ░č▓mż╣żļż╚ż╚żŌż╦ĪóAdvanced Backend Fab 7ż“±śŽč┘ĀʬĖ®ż╦2024ŃQ¼Źż▐żŪż╦ÅŚ╣®ż╣żļż│ż╚ż╦żĘżŲżżżļż█ż½ĪóAdvanced Backend Fab 8ż“±śŽč▓┼▒IĖ®ż½Ų▐╬ėĖ®ż╦Ę·└▀ż╣żļż│ż╚ż“ĖĪŲżżĘżŲżżżļĪŻ

Ī╩ÅRĪ╦CoWoSĪ¦Chip on Wafer on Substrateż╬ŠSĪŻ2012ŃQż╦TSMC╝ęż╦żĶż├żŲ│½╚»żĄżņż┐╣Ō└Łē”ź┴ź├źūĖ■ż▒╣Ō╠®┼┘źčź├ź▒Ī╝źĖź¾ź░Č\ĮčĪŻNvidiaż╬AI ź┴ź├źūź╗ź├ź╚ż╬╝┬äóż╦¾H├ōżĄżņżŲż¬żĻĪóTSMCżŪżŽÖ┌ŠÅż¼╝{żżż─ż½ż║Īó▐kŗOSATż╦×æļ]░č▓mżĘżŲżżżļĪŻ╣Įļ]╬Ńż“┐▐2║Ė▓╝ż╦┐āż╣ĪŻ

Øi╣®µćż╚ĖÕ╣®µćż“ŲDżĻĘeż─Īų├µ╣®µćĪūż╚żŽĪ®

“£═Ķ╚ŠŲ│öü×æēäż╬ĖÕ╣®µćżŽĪ󱜎čż╦¾H┐¶┘T║▀ż╣żļOSATż¼╩¼├┤żĘżŲżŁż┐ż¼ĪóAIź┴ź├źūżŽżĖżß└Ķ├╝╚ŠŲ│öü×æēäż╬ĖÕ╣®µćżŽ╩Ż╗©żŪĪó╚ļ╠®╩▌ĘeæųĪóźšźĪź”ź¾ź╔źĻ╝ęŲŌżŪ╣įż”ź▒Ī╝ź╣ż¼╗\ż©żŲżżżļĪŻ

ź┴ź├źūźņź├ź╚ż╬┼ąŠņżŪĪóØi╣®µćż╚ĖÕ╣®µćż╬ČŁ─cż¼żóżżż▐żżż╦ż╩żĻĪóź┴ź├źūźņź├ź╚┤ųż“źĘźĻź│ź¾źżź¾ź┐Ī╝ź▌Ī╝źČĪ╝żõźųźĻź├źĖź┴ź├źūż“├ōżżżŲ└▄¶öż╣żļż╦żŽØi╣®µćż╬Č\Įčż¼ØŁ═ūż└żĘĪó┼┼Ė╗ČĪĄļż“╬óĀCż½żķ╣įż”Īóżżż’żµżļ ╬óĀC┼┼Ė╗ČĪĄļź═ź├ź╚ź’Ī╝ź»Ī╩BSPDNĪ╦ż“Ę┴└«ż╣żļż┐żßż╬ź”ź¦Ī╝źŽČ╦Ū÷▓Įż╦żŽĖÕ╣®µćż╬Č\Įčż¼ØŁ═ūż╚ż╩żļĪŻØi╣®µćż╚“£═Ķż╬ĖÕ╣®µćż╬├µ┤ųż╦░╠ÅøżĘĪóØi╣®µćż╚ĖÕ╣®µćż╬Č\Įčż¼║«║▀ż╣żļ╣®µćż“Īó║ŪŖZĪų├µ╣®µćĪūż╚▐kŗżŪŌ}żążņżļżĶż”ż╦ż╩ż├ż┐ĪŻ║ŻĖÕĪó3D-IC╝┬ĖĮż╬═ūż╚ż╩żļ├µ╣®µćż¼śŗż╦ÅRų`żĄżņżļżĶż”ż╦ż╩żļż└żĒż”ĪŻ

ż┐ż└żĘĪóĪų├µ╣®µćĪūż╬─Ļ▒IżŽżóżżż▐żżżŪżóżļĪŻźŪźŻź╣ź│żŽĪóŲ▒╝ęż¼├┤┼÷ż╣żļź░źķźżź¾źŪźŻź¾ź░Ī╩Ė”║’ż╦żĶżļź”ź¦Ī╝źŽż╬Ū÷▓ĮĪ╦ż½żķź└źżźĘź¾ź░Ī╩└┌║’ż╦żĶżļź”ź¦Ī╝źŽż╬Ė─╩ę▓ĮĪ╦ż▐żŪż╬╣®µćż“Īų├µ╣®µćĪūż╚Ō}żėĪóźóź├ź╗ź¾źųźĻ░╩æTż╬ĖÕ╣®µćż╚ČĶ╩╠żĘżŲżżżļż¼Īóż│żņżŽŲ▒╝ęŲ╚śOż╬─Ļ▒IżŪżóżļĪŻ

ÖÄ┘ćż╚Š╩¾śŗ┐Ę

WaferTechżŽTSMC Washingtonż╦╝ęć@╩čśŗ

ØiövĘŪ║▄żĘż┐TSMCŠņŗ▐k═„żŪFab 10ż╚Fab 11ż¼Ų■żņ░Ńż├żŲżżż┐ż╬żŪĪó░╩▓╝ż╬żĶż”ż╦ÖÄ┘濥ż╗żŲżżż┐ż└ż»ĪŻ

Fab 10ĪĪ├µ╣±Ī”æųķL

Fab 11ĪĪä▌╣±ź’źĘź¾ź╚ź¾ä”

ż╩ż¬ĪóFab 11żŽĪóWaferTechż╚żżż”╝ęć@ż└ż├ż┐ż¼Īó2023ŃQ12ĘŅ15Ų³ĪóTSMC Washingtonż╚╝ęć@╩čśŗżĘż┐ĪŻŲ▒╝꿎Īó1996ŃQż╦TSMCż╚Analog DevicesĪ╩ADIĪ╦ĪóIntegrated Silicon Solution IncĪ╩ISSIĪ╦Ī󿬿ĶżėAlteraĪ╩ĖĮIntelĪ╦ż╬╣ń╩█▓±╝ęż╚żĘżŲĪóä▌╣±Įķż╬200mm└ņČ╚źšźĪź”ź¾ź╔źĻż╚żĘżŲ├┬Ö┌żĘż┐ĪŻ2010ŃQż╦TSMCż╬100%╗ę▓±╝ęż╚ż╩ż├ż┐ż¼Īó╝ęć@żŽ╩čśŗżĄżņż║ż╦żżż┐ĪŻ║Żövż╬╝ęć@╩čśŗżŽĪóż│ż╬źšźĪźųż¼TSMCż╬╗▒▓╝ż╦żóżļż│ż╚ż“╝■ē¶żĘĪóźóźĻźŠź╩ż╦┐Ę╣®ŠņĘ·└▀├µż╬TSMCż╬ä▌╣±ż╦ż¬ż▒żļ┘T║▀┤Čż“żĄżķż╦źóźįĪ╝źļż╣żļ┴└żżż¼żóżļż╚Ė└ż’żņżŲżżżļĪ╩╗▓╣═½@╬┴3Ī╦ĪŻ

╗▓╣═½@╬┴

1. └Kŗō·ĪóĪų±śŽčTSMC╝ęż╬źšźĪźų23żŽż╔ż│ż╦żóżļĪ®źšźĪźų23źšź¦Ī╝ź║1ż╚żŽ▓┐Ī®ĪūĪóĪĪź╗ź▀ź│ź¾ź▌Ī╝ź┐źļ (2023/12/12)

2. └Kŗō·ĪóĪųTSMCż╬▓±─╣ż¼Ėņż├ż┐3D ICČ\Įčż╬ĖĮėXż╚Įø═Ķ·t╦Š - ISSCC 2021ĪūĪóź▐źżź╩źėź╦źÕĪ╝ź╣TECH+ (2021/02/25)

3. └Kŗō·ĪóĪųTSMCĪóä▌╣±╗ę▓±╝ęż╬WaferTechż╬╝ęć@ż“TSMC Washingtonż╦╩čśŗĪūĪóź▐źżź╩źėź╦źÕĪ╝ź╣TECH+ (2023/12/21)